Test set reordering method and device based on estimated test performance of testable area

A technology for testing performance and test sets, applied in the direction of electronic circuit testing, automated testing systems, etc., can solve problems such as low test performance, and achieve the effect of reducing test time, simple method, and shortening fault detection time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0038] First of all, it needs to be explained that, regardless of the design defects of the integrated circuit itself or the loopholes in the manufacturing process, the occurrence of failures is a small probability event, the occurrence of failures is relatively independent, and the failure rate is relatively stable, that is, the occurrence of failures obeys Poisson distribution. Assume that an existing integrated circuit X contains n logic gates. In the standard cell library (in the integrated circuit manufacturing process, different manufacturing processes use different standard cell libraries, and the length, length, and Width.) The length and width of each type of logic gate are known. In the actual test, the test vectors have the characteristics that they can be merged and the order cannot be adjusted.

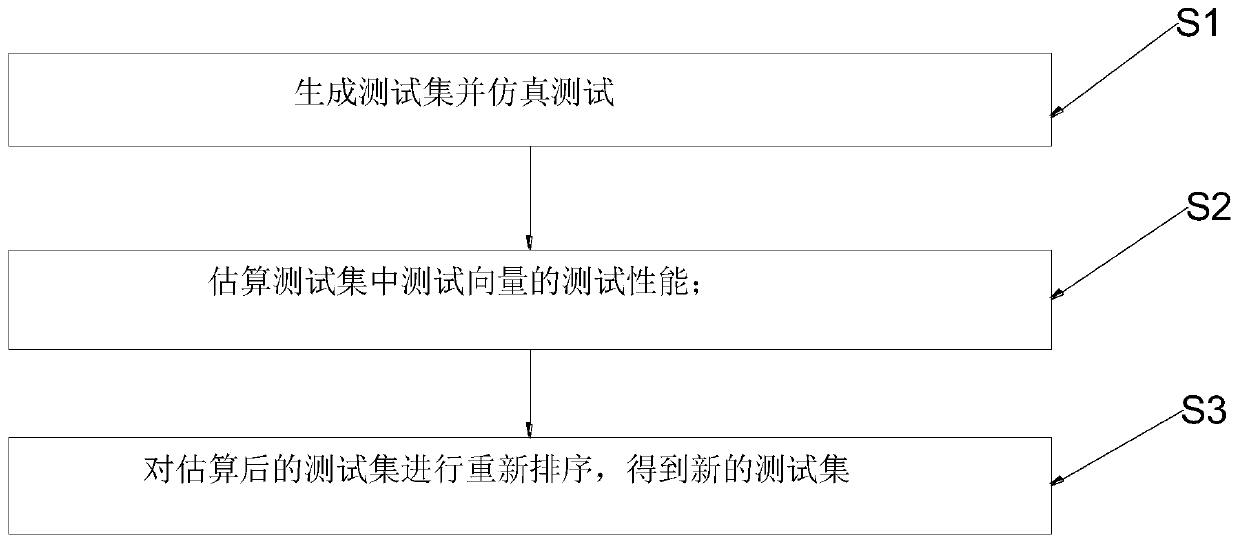

[0039] Such as figure 1 , a test set reordering method based on estimating test performance, including the following steps:

[0040] S1. Generate a test set and simulat...

Embodiment 2

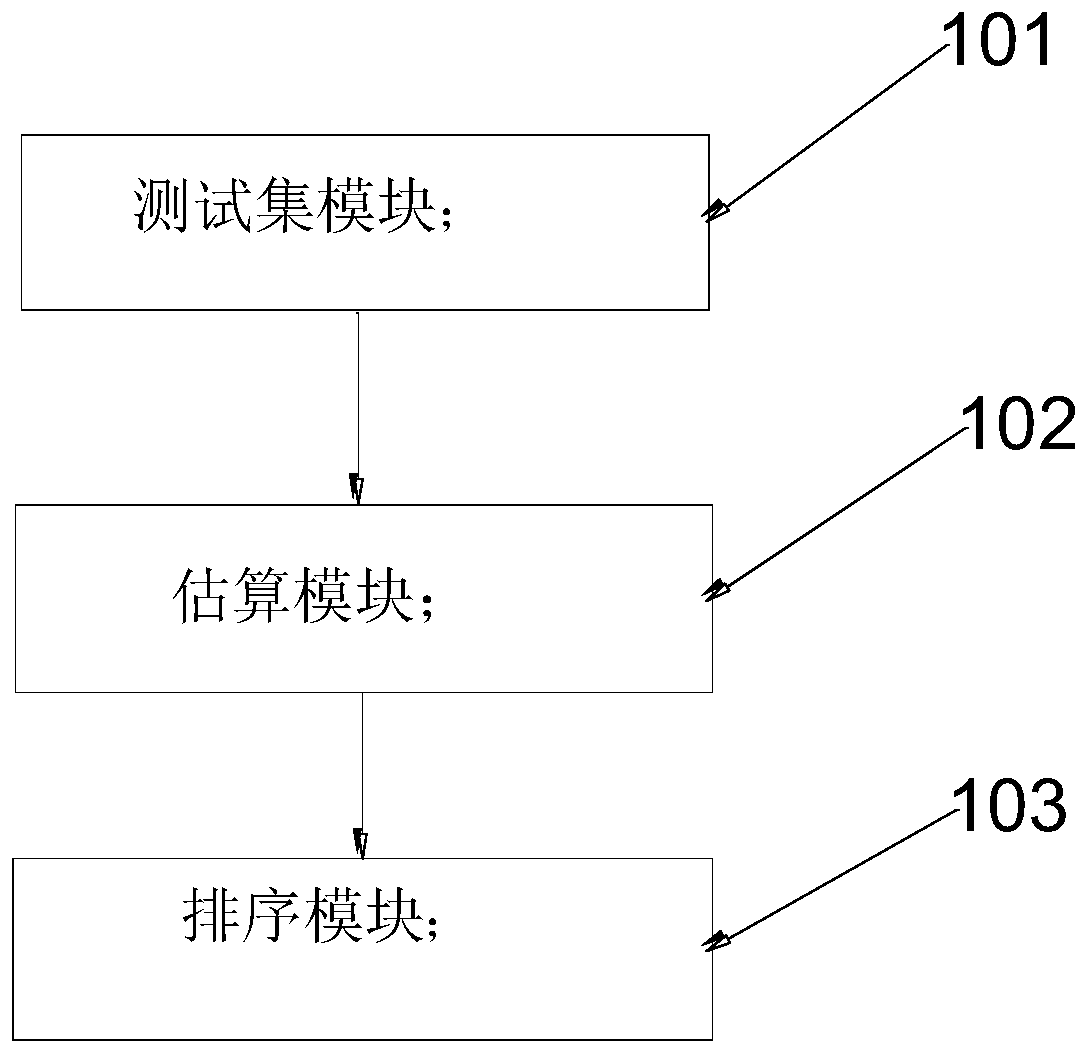

[0063] A sorting device for a test set reordering method based on estimating test performance, comprising:

[0064] The test set module is used to generate test sets and simulate tests;

[0065] Also includes the following steps:

[0066] S11, using an automatic test generation algorithm to make the integrated circuit X generate a test set V of the Y test type 1 ,V 2 ,...,V i ,...,V n , including input sequence and output sequence; because there are n types of faults to be tested in actual testing, it is necessary to generate n types of test sets;

[0067] In this embodiment, the automatic test generation algorithm is an existing technology, and will not be described in detail here.

[0068] S12. Analyze the logic gate structure inside the integrated circuit X, and build a simulation environment to restore the logic gate structure through programming to perform fault simulation testing;

[0069] When testing, sequentially use the test set V 1 ,V 2 ,...,V i ,...,V m E...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More