Shift register, gate driving circuit, display panel and display device

A shift register and gate technology, which is applied in the field of shift registers, display panels, display devices, and gate drive circuits, and can solve the problems of large leakage current, leakage current, and incomplete closing of transistors in PMOS

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, but not to limit the present invention. In addition, it should be noted that, for the convenience of description, only some structures related to the present invention are shown in the drawings but not all structures.

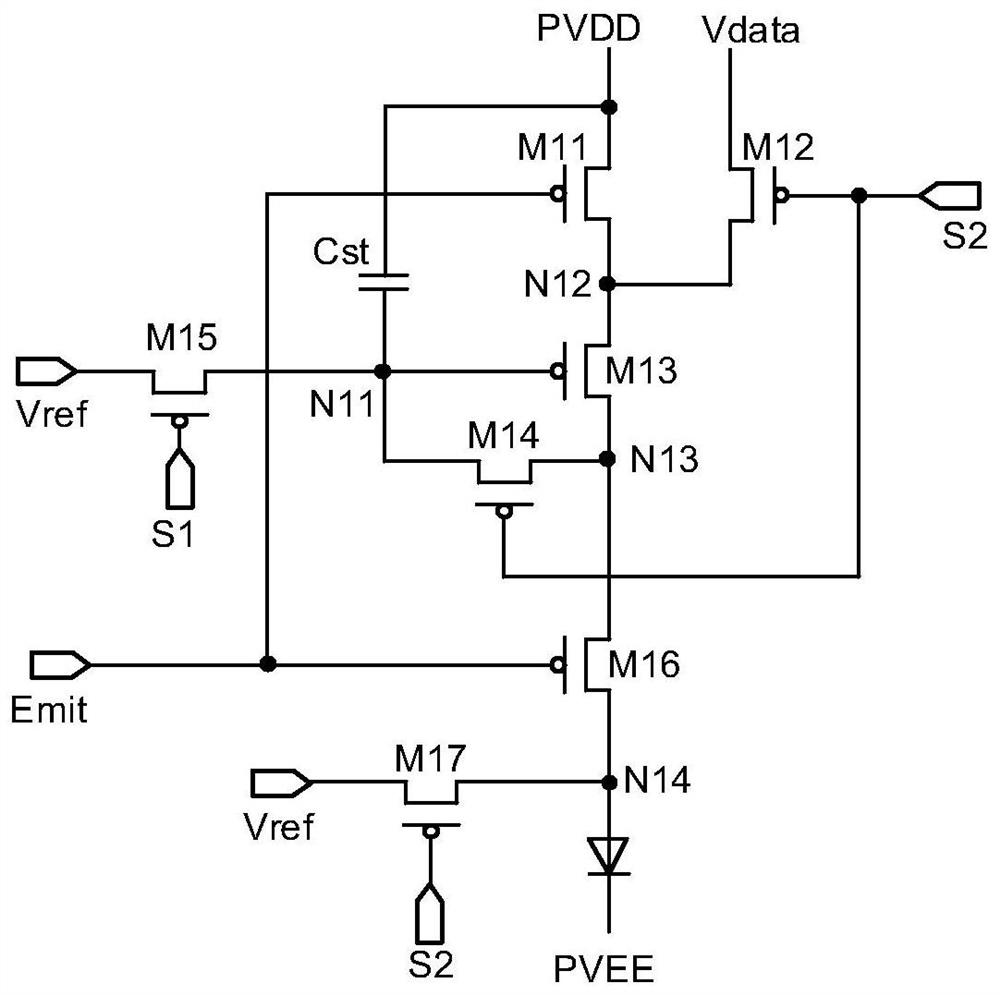

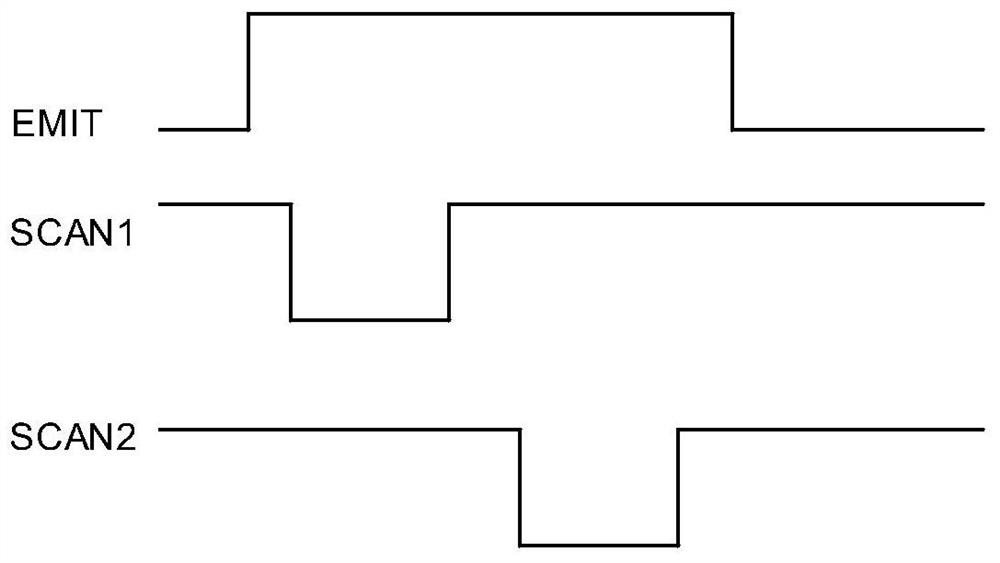

[0051] figure 1 It is a schematic circuit diagram of a pixel driving circuit in the related art, which shows a PMOS designed pixel driving circuit; figure 2 for figure 1 Schematic diagram of driving timing of an exemplary pixel driving circuit, wherein the low-level signal is an enabling signal. refer to figure 1 and figure 2 , the first scanning signal SCAN1 represents the control signal received by the first scanning signal terminal S1, the second scanning signal SCAN2 represents the control signal receive...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More