Instruction scheduling method and system for multi-cycle instruction and medium

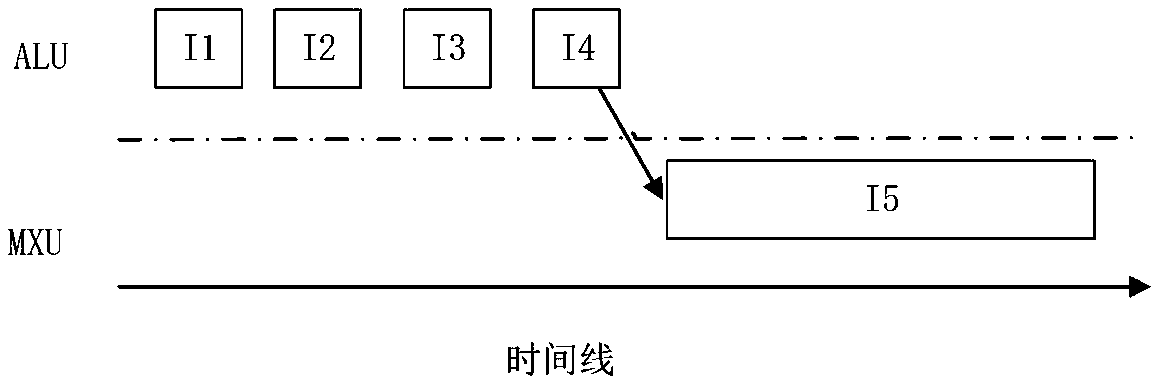

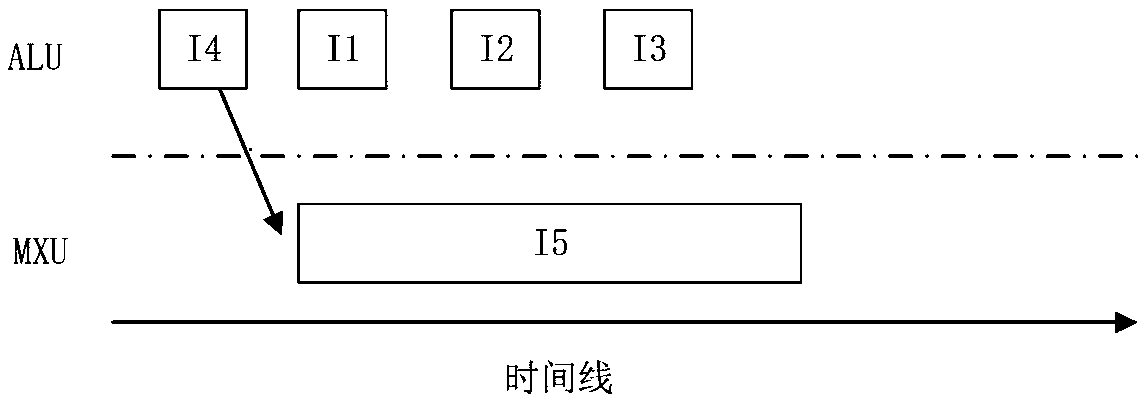

An instruction scheduling, multi-cycle technology, applied in concurrent instruction execution, program control design, instrumentation, etc., can solve the problem that instruction I5 cannot instruct parallel instructions, instruction I5 source operands are not ready, etc., to achieve low overhead and improve performance. , easy to achieve effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

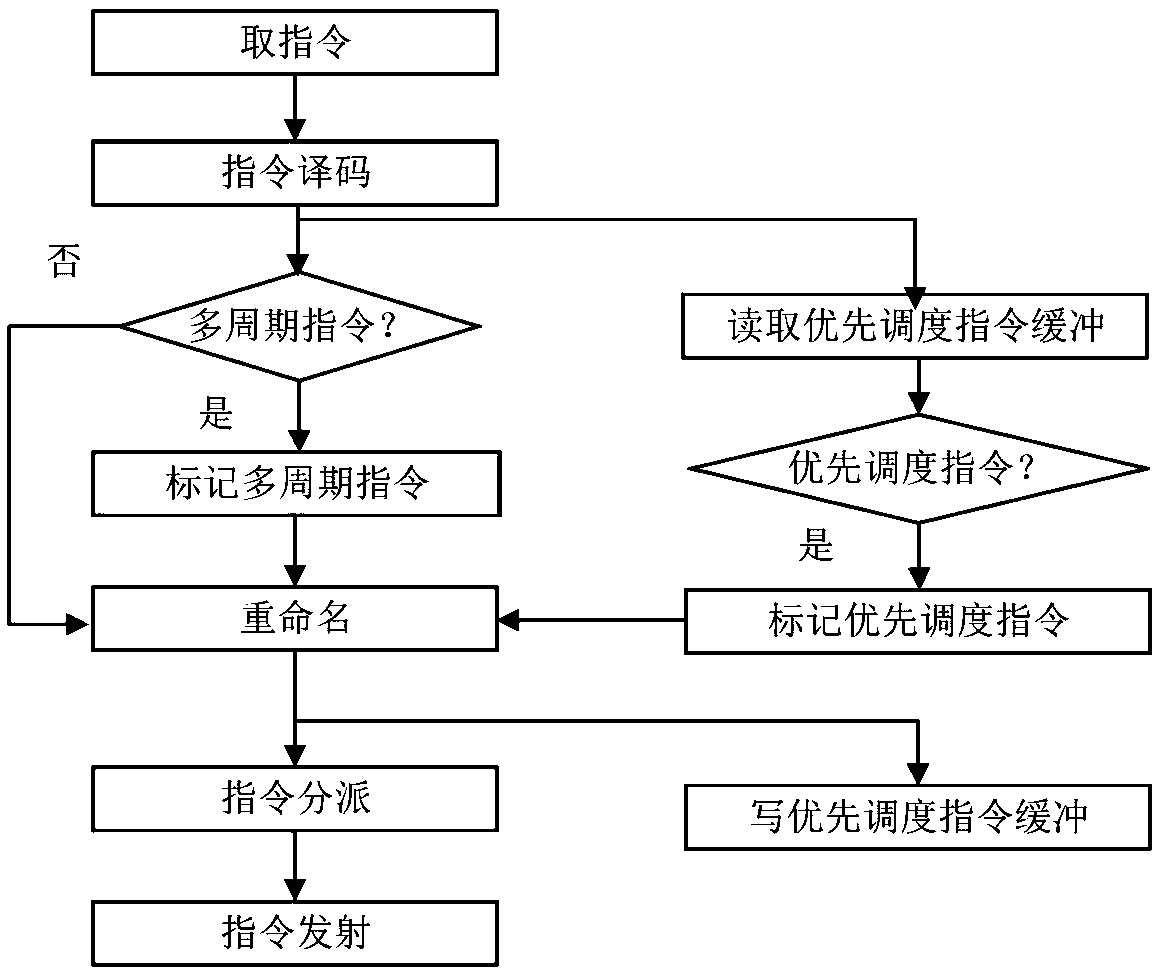

[0036] Such as figure 2 As shown, the implementation steps of the instruction scheduling method for multi-cycle instructions in this embodiment include:

[0037] 1) Fetch the current instruction; fetch the instruction from the instruction buffer or the next-level storage, this step is the instruction fetching process of a common processor, and there is no need to modify the existing method;

[0038] 2) During instruction decoding, the operand and opcode of the current instruction are decoded; in the instruction decoding stage, the instruction operand and opcode are decoded. This step is consistent with the decoding process of ordinary processors, and there is no need to Modifications to existing methods;

[0039] 3) Use the opcode to identify whether the current instruction is a multi-cycle instruction, if it is a multi-cycle instruction, mark the current instruction as a multi-cycle instruction, and identify the dependent instructions of the current instruction; at the same...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More