Memory and method of forming the same

A technology of memory and predetermined direction, which is applied in the manufacture of semiconductor devices, electrical solid-state devices, semiconductor/solid-state devices, etc. It can solve the problems of increased risk of short circuit, residual active area, and very large limitation of photolithography process window. Achieve the effect of reducing the risk of short circuit, simplifying the process and increasing the process window

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

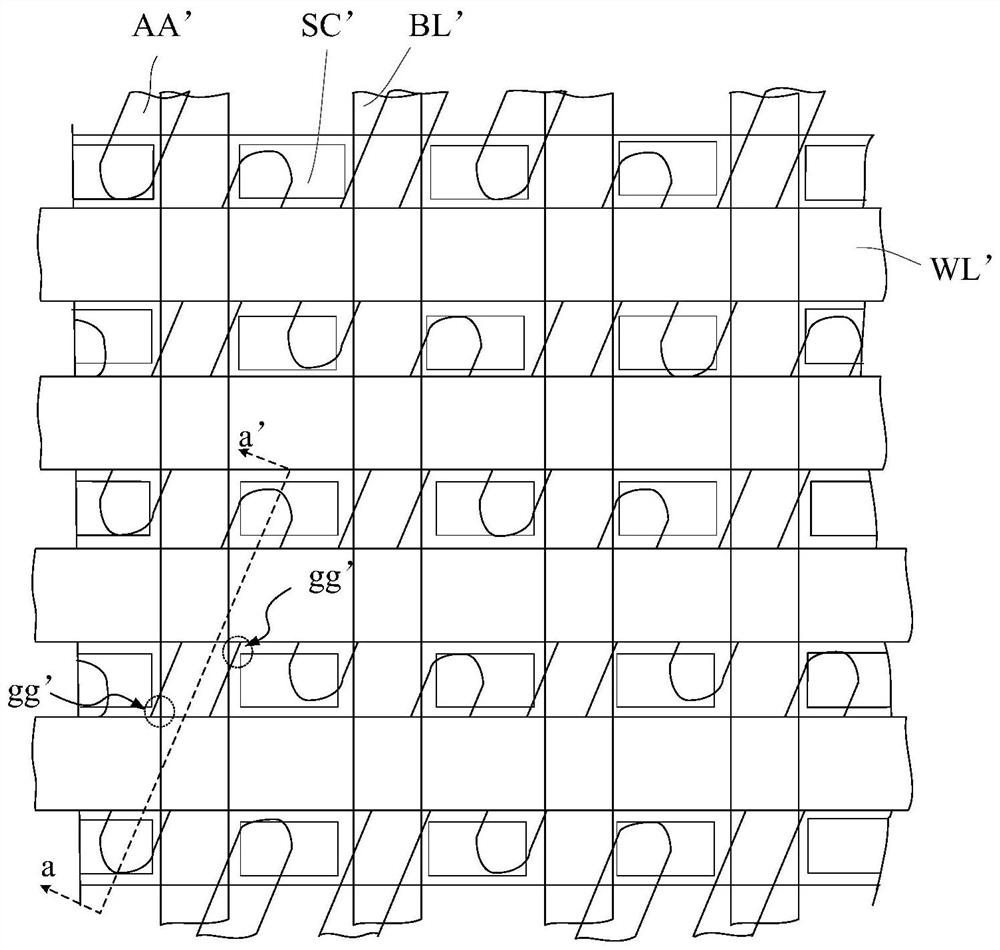

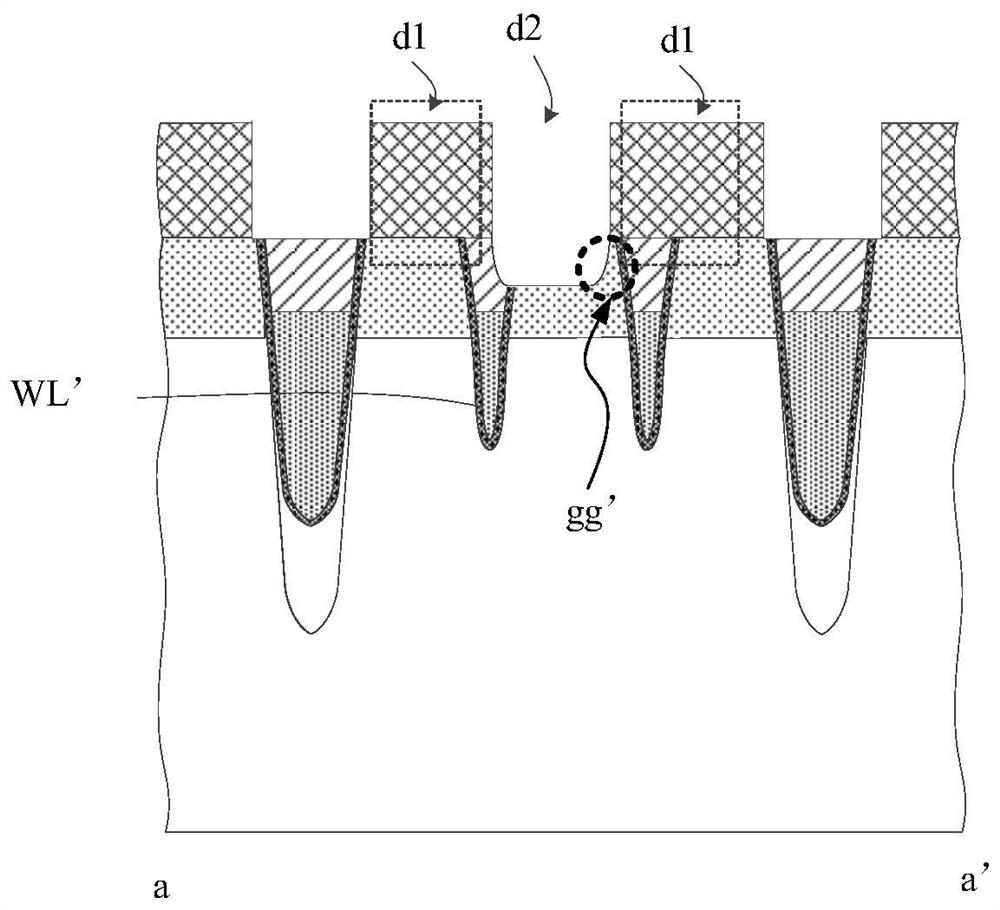

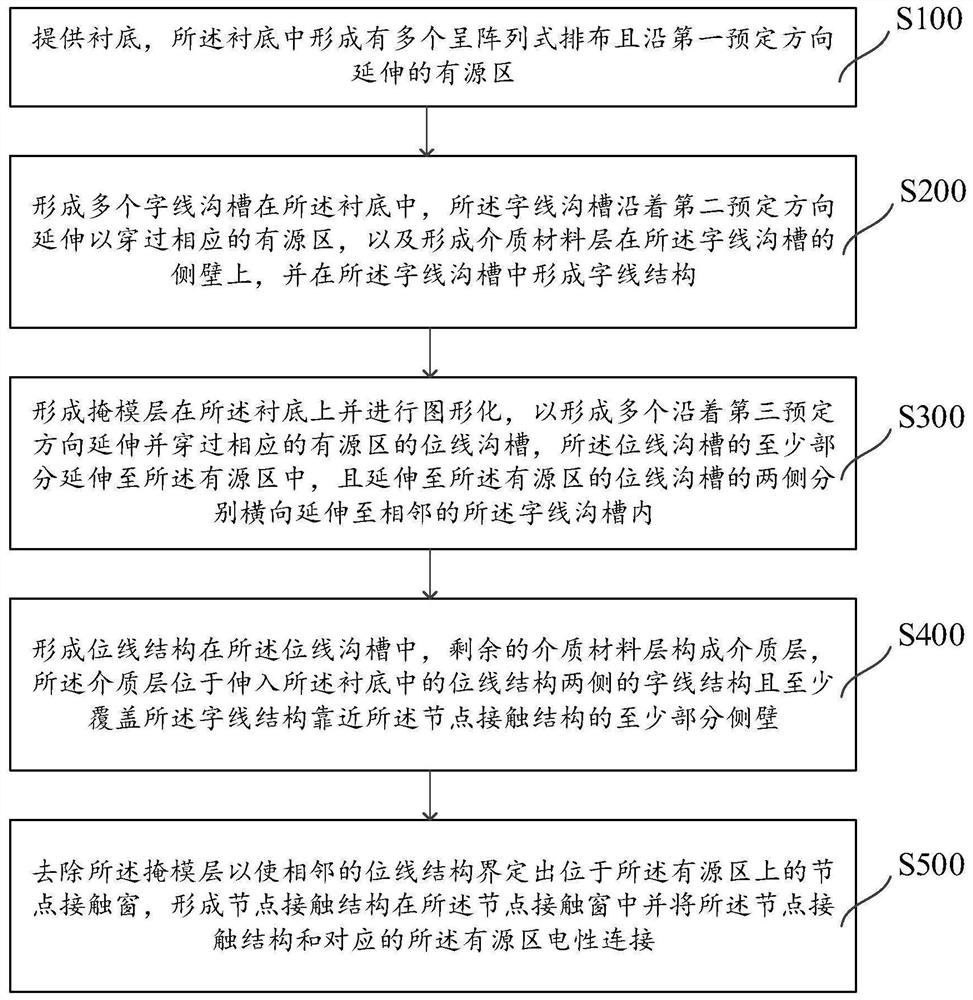

[0064] Figure 4f A schematic diagram of a partial structure of the memory in the first embodiment of the present invention, Figure 4g for Figure 4f Simplified layout of the memory in the Figure 4f for Figure 4g Schematic cross-sectional view of the memory in the a-a' direction. like Figure 4f as well as Figure 4g As shown, the memory includes: a substrate 100 and a word line structure WL formed in the substrate 100 .

[0065] A plurality of active regions AA and trench isolation structures STI are formed in the substrate 100 extending along a first predetermined direction (Z direction), and the trench isolation structures STI separate adjacent active regions AA. A plurality of the active areas AA are arranged in an array, and the active areas AA are independent of each other through the trench isolation structure STI, so as to avoid mutual interference between the active areas AA.

[0066] Further, word line trenches are also formed in the substrate 100, and the ...

Embodiment 2

[0142] Figure 5a It is a schematic diagram of a partial structure of the memory in the second embodiment of the present invention, Figure 5b for Figure 5a Simplified layout of the memory in the Figure 5a for Figure 5b Schematic cross-sectional view of the memory in the a-a' direction. like Figure 5a as well as Figure 5b As shown, the difference from the first embodiment is that in this embodiment, the dielectric layer only covers at least part of the sidewall of the second word line structure WL2 close to the node contact structure SC. That is to say, the dielectric layer only includes the first sidewall SP1.

[0143] Specifically, as Figure 5a As shown, the first spacer SP1 extends from the bottom of the node contact structure SC to a third depth position H3 ′ in the substrate 100 , that is, the top of the first spacer SP1 is located at the first At the depth position H1', the first sidewall spacer SP1 extends from the first depth position H1' along the firs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More