Array substrate, display panel and manufacturing method of array substrate

A technology for array substrates and manufacturing methods, which is applied in the display field and can solve problems affecting product quality, cracks in passivation layers, and thin-film transistor devices that cannot realize normal charging and discharging of pixels, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

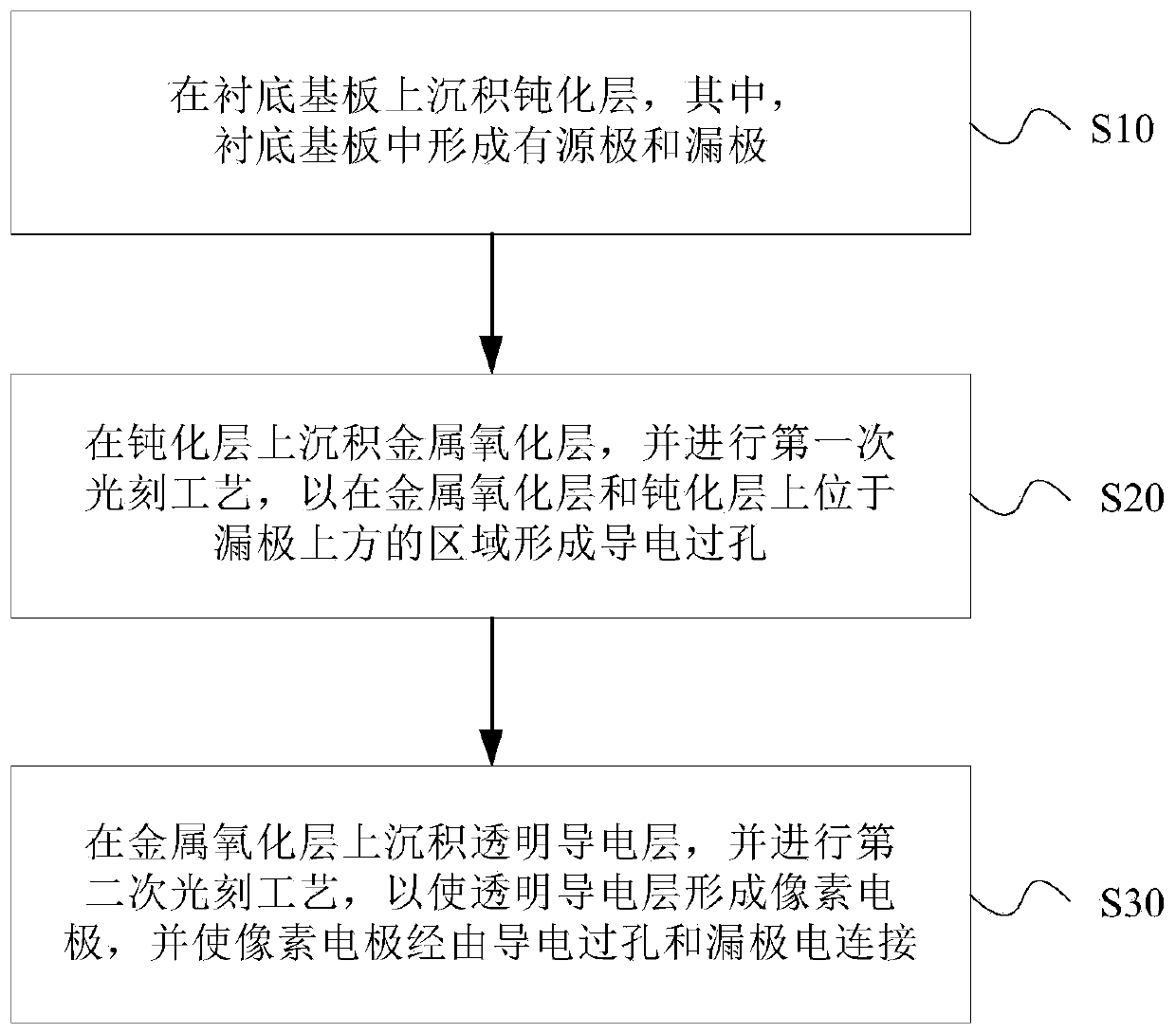

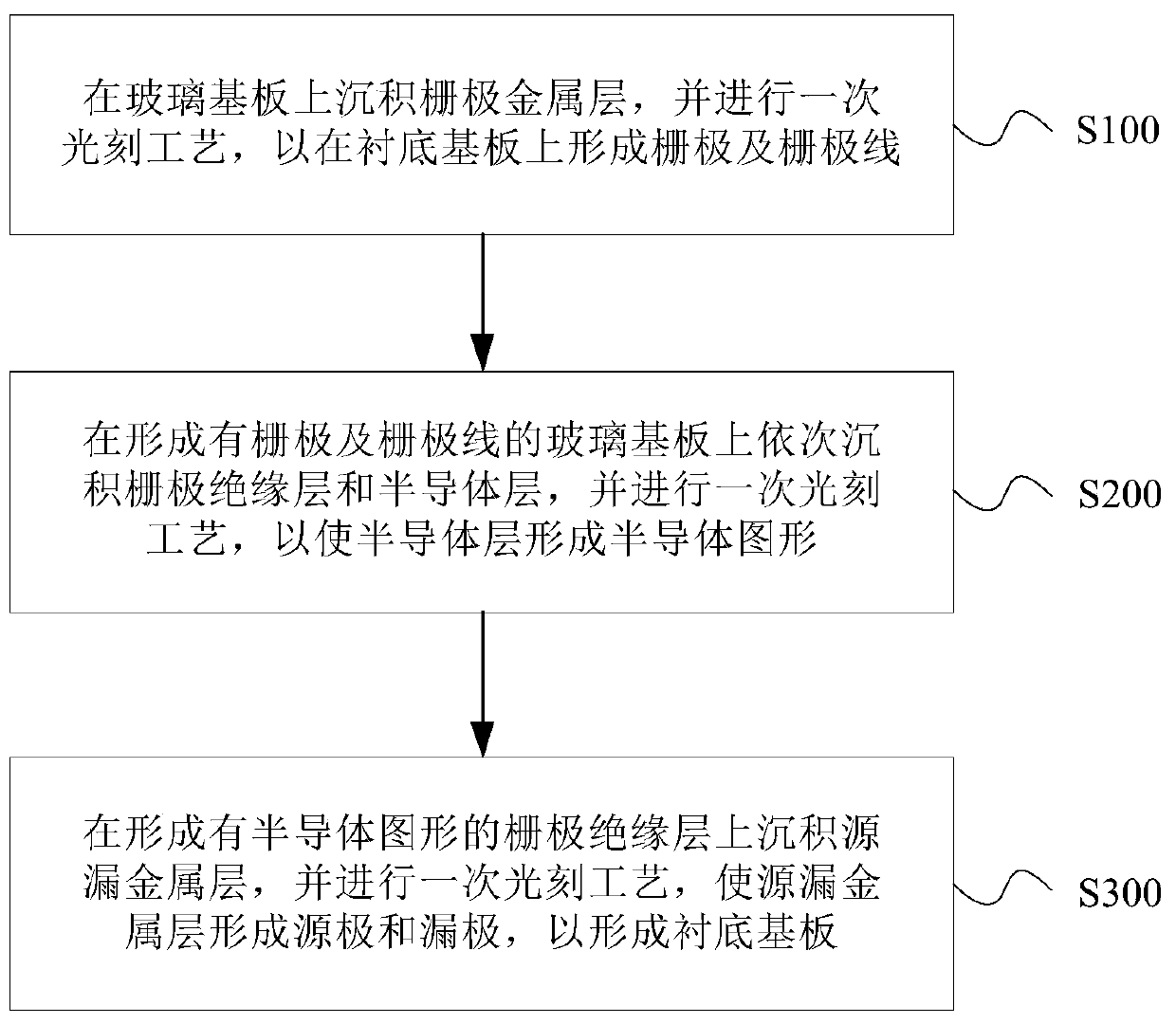

[0038] figure 1 It is a schematic flow chart of the manufacturing method of the array substrate provided by Embodiment 1 of the present invention.

[0039] In the embodiment of the present application, the thin film transistors in the array substrate may be top-gate or bottom-gate thin film transistors, and in the thin film transistors, the semiconductor pattern may be a metal oxide semiconductor pattern or a low temperature polysilicon semiconductor pattern. In other words, in the array substrate in this application, the thin film transistors can be of various types and formation methods, as long as a passivation layer and pixel electrodes are formed on the substrate substrate, the technical solutions in this application can be used to solve the problems in the passivation layer. There is a problem that cracks cause over-etching of the semiconductor layer.

[0040] refer to figure 1 , the manufacturing method of the array substrate of the present invention comprises:

[0041...

Embodiment 2

[0078] This embodiment provides an array substrate 100, which is manufactured by the manufacturing method described in Embodiment 1. Figure 10 A schematic structural diagram of the array substrate 100 provided in Embodiment 2 of the present invention.

[0079] refer to Figure 10 , the array substrate 100 includes: a base substrate 10 and a passivation layer 20, a metal oxide layer 30, and a pixel electrode 50 sequentially formed on the base substrate 10, and a The conductive via hole 31 , the conductive via hole 31 penetrates the passivation layer 20 and the metal oxide layer 30 , and the pixel electrode 50 is electrically connected to the drain electrode 16 through the conductive via hole 31 .

[0080] In the above solution, a layer of metal oxide layer 30 is formed on the passivation layer 20 as a strengthening layer of the passivation layer 20, which can prevent the chemical solution for etching the pixel electrode 50 from penetrating into the semiconductor layer, and av...

Embodiment 3

[0095] This embodiment provides a display panel, including the array substrate 100 in the second embodiment, wherein the specific structure and functions of the array substrate 100 have been described in detail in the second embodiment above, and thus will not be repeated here.

[0096] The display panel may be a liquid crystal display panel. In this case, the display panel includes a color filter substrate, a liquid crystal layer, and the array substrate 100 described in Embodiment 2, and the liquid crystal layer is interposed between the color filter substrate and the array substrate 100 .

[0097] The display panel may also be an organic light emitting diode display panel. In this case, the display panel includes the array substrate 100 described in Embodiment 2, an encapsulation layer and an organic layer, wherein the organic layer is interposed between the array substrate 100 and the encapsulation layer.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More