Correction method suitable for two-step ADC

A correction method and slope technology, applied in analog/digital conversion calibration/testing, signal transmission systems, instruments, etc., can solve problems such as overall accuracy impact, voltage reduction, and impact on the correctness of quantization results.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0060] The technical solution of the present invention will be further described through the embodiments below in conjunction with the accompanying drawings.

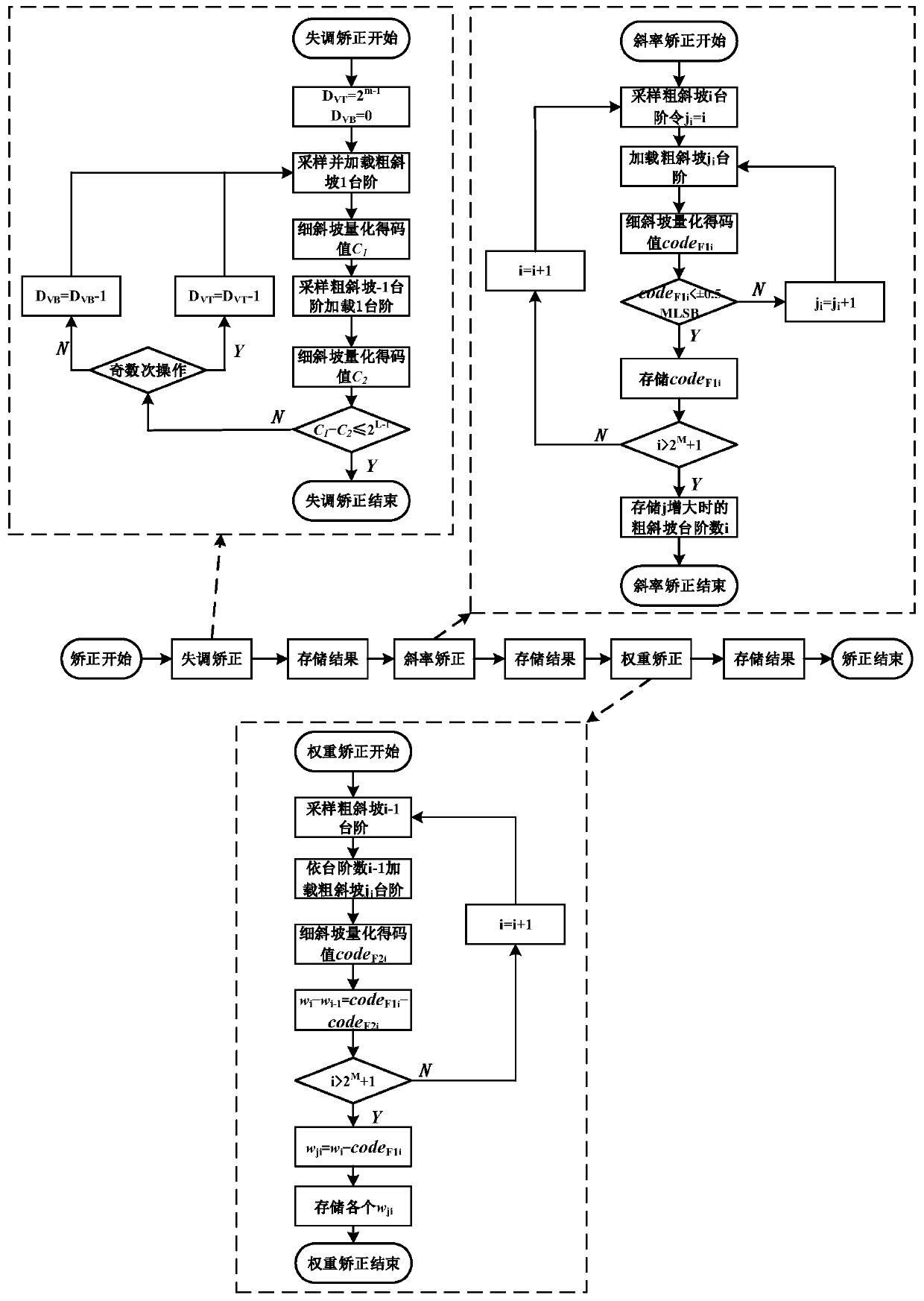

[0061] Such as image 3 Shown is a logic block diagram of a correction method suitable for two-step ADC proposed by the present invention. The correction method proposed by the present invention works before the normal quantization of the two-step ADC, including correcting fine slope clamping operational amplifier offset, correcting There are three parts of coarse slope slope and corrected coarse slope weight, including the following steps:

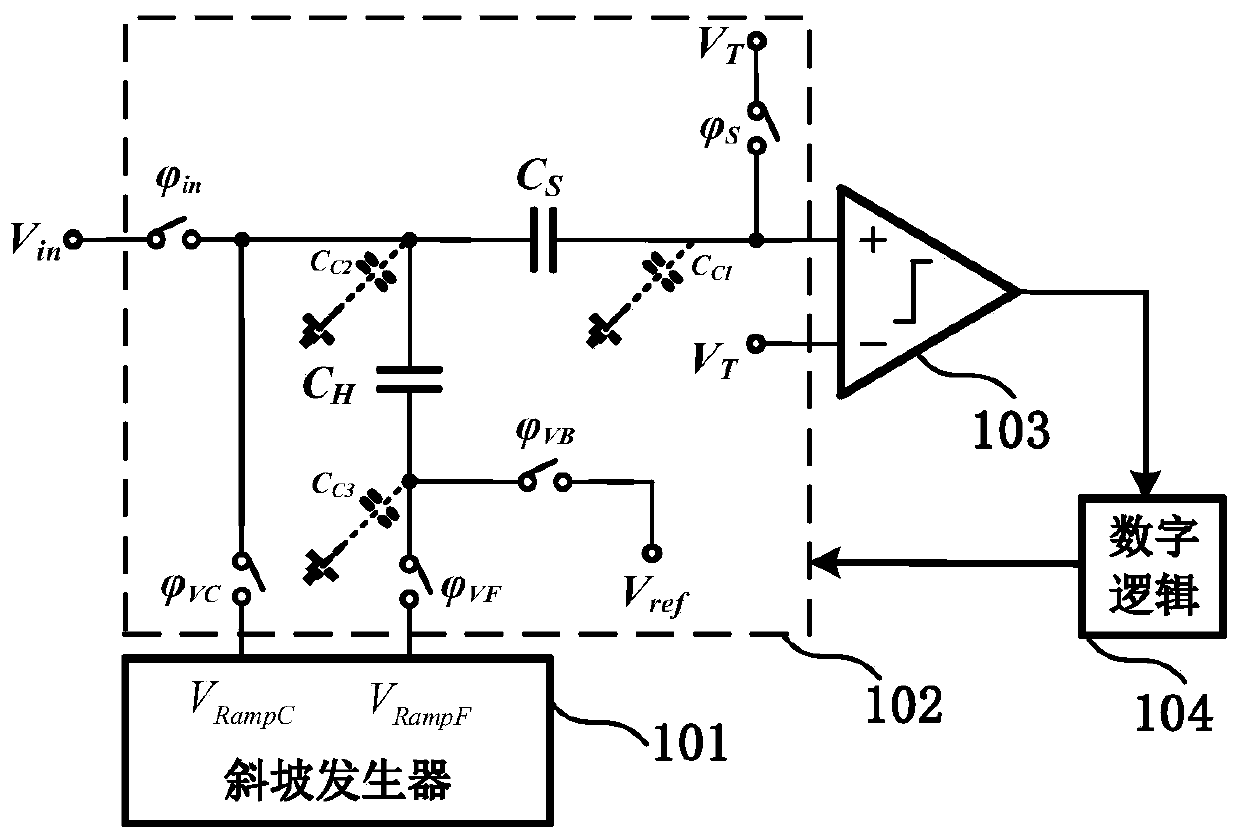

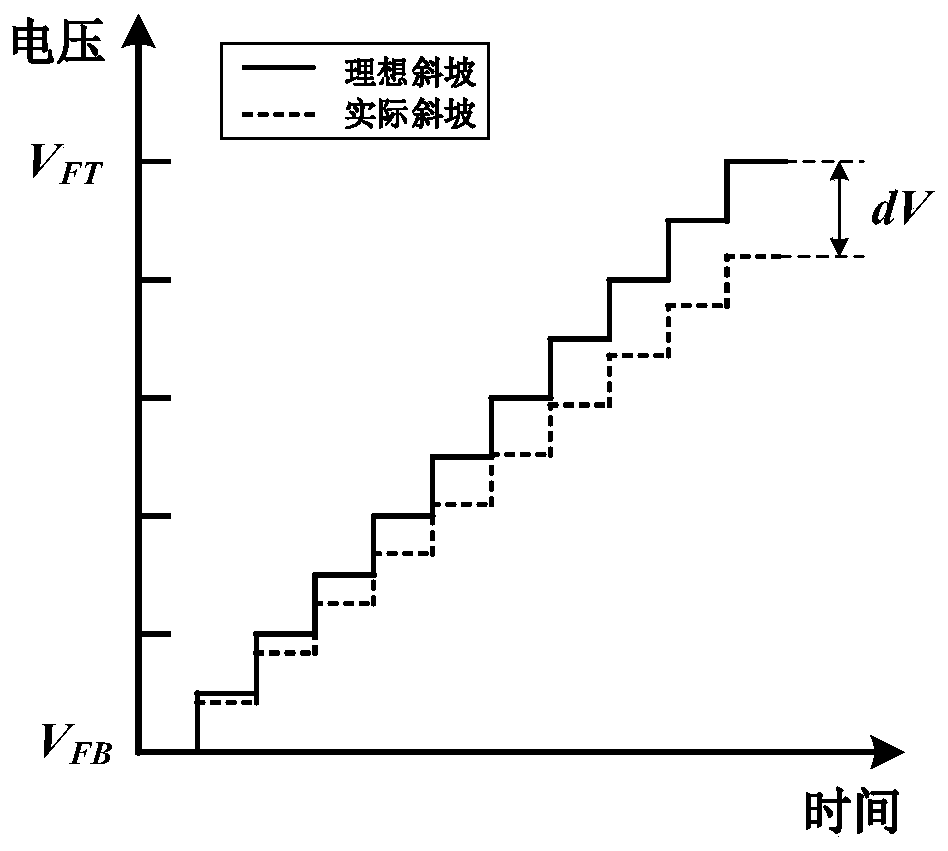

[0062] Step 1. Before the quantization of the two-step ADC starts, correct the offset of the clamping op-amp of the thin ramp generating unit. Such as Figure 4 Shown is a schematic circuit diagram of the ramp generator, including a thick ramp generating unit 401 and a fine ramp generating unit 402, wherein the thick ramp completes the quantization of the high M bits, the fine ra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More