Low-voltage ESD protection device and manufacturing method thereof

A technology of ESD protection and manufacturing method, which is applied in the field of electronic science and technology, can solve the problems of high ESD trigger voltage, low current density, high ESD, etc., and achieve the effect of reducing chip area occupation, reducing chip cost, and optimizing device size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

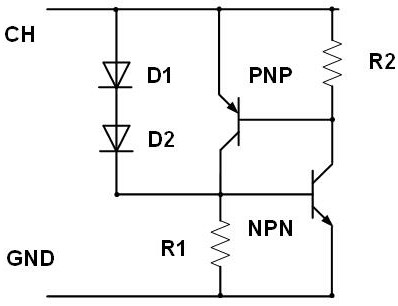

[0037] Such as Figure 1-15 As shown, a low-voltage ESD protection device includes an N-type single crystal material layer 101, an N+ polysilicon 103, an N-type base region 104, and a P-type base region 105. The N-type single crystal material layer 101 is provided with a first layer of isolation medium 108. The first metal layer 109, the second layer of isolation dielectric 110, the second metal layer 111, the N+ polysilicon 103, the N-type base region 104, and the P-type base region 104 are all set on the top of the N-type single crystal material layer 101, and the N+ polysilicon 103 is provided with a P+ source region 106 and an N+ source region 107, a thermal oxide layer 102 is provided between the outside and the N-type single crystal material layer 101, and a P+ source region 106 and a P-type base region 105 are provided in the N-type base region 104. A P+ source region 106 , an N+ source region 107 , an N+ source region 107 , and a P+ source region 106 are sequentially a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More