Chip welding structure and welding method

A chip welding and chip technology, applied in the field of chip welding structure and welding, can solve the problems of chip internal structure damage, high packaging cost, large chip impact, etc., and achieve the effect of reducing impact force, production cost, and impact force.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

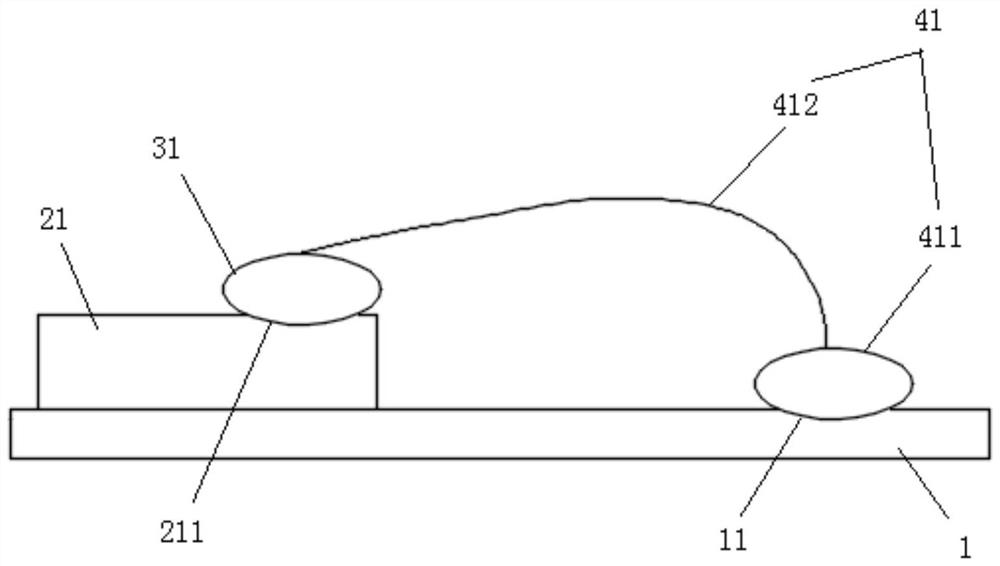

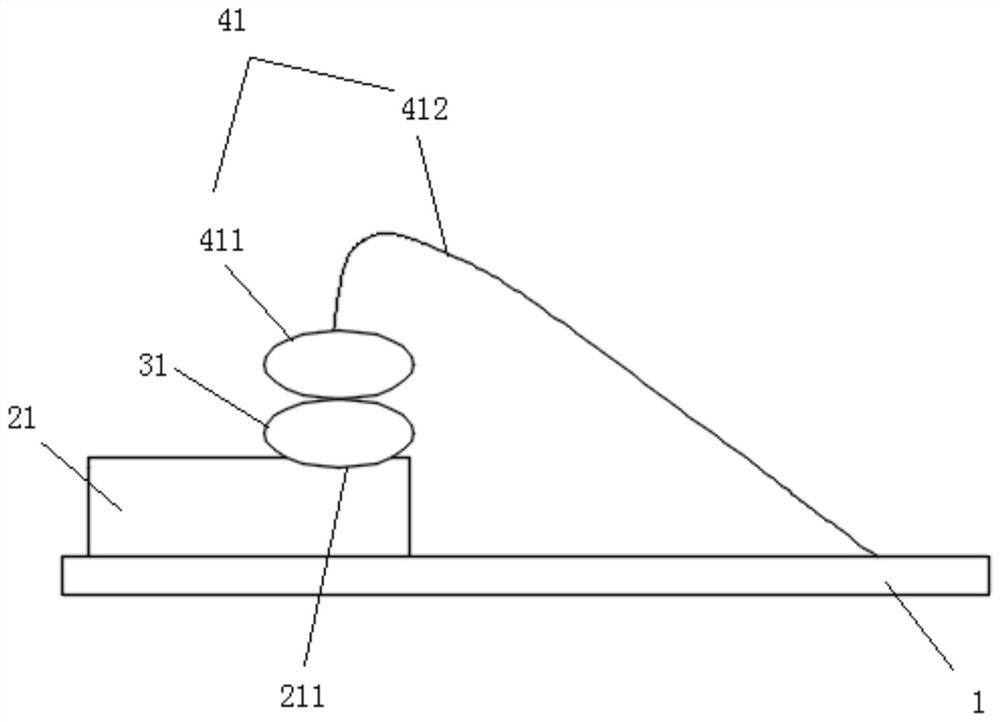

[0043] Such as figure 1 , figure 2 As shown, the chip bonding structure of this embodiment realizes the electrical connection between a single chip and the substrate, including: the substrate 1 , the first chip 21 , the first gold pad 31 and the first copper connection wire 41 .

[0044] The first chip 21 is disposed on the upper surface of the substrate 1 .

[0045] The first gold pad 31 is disposed on the upper surface of the first chip 21 , and the first gold pad 31 is located at one end of the first chip 21 .

[0046] The first copper connection line 41 includes: a first copper welding point 411 and a first copper welding line 412 .

[0047] The first copper pad 411 is located at one end of the first copper wire 412, and the other end of the first copper pad 411 and the first copper wire 412 are connected to the first gold pad 31 on the first chip 21 and the substrate 1 respectively. The connection is through the first copper pad 411 and the first copper wire 412 , so ...

Embodiment 2

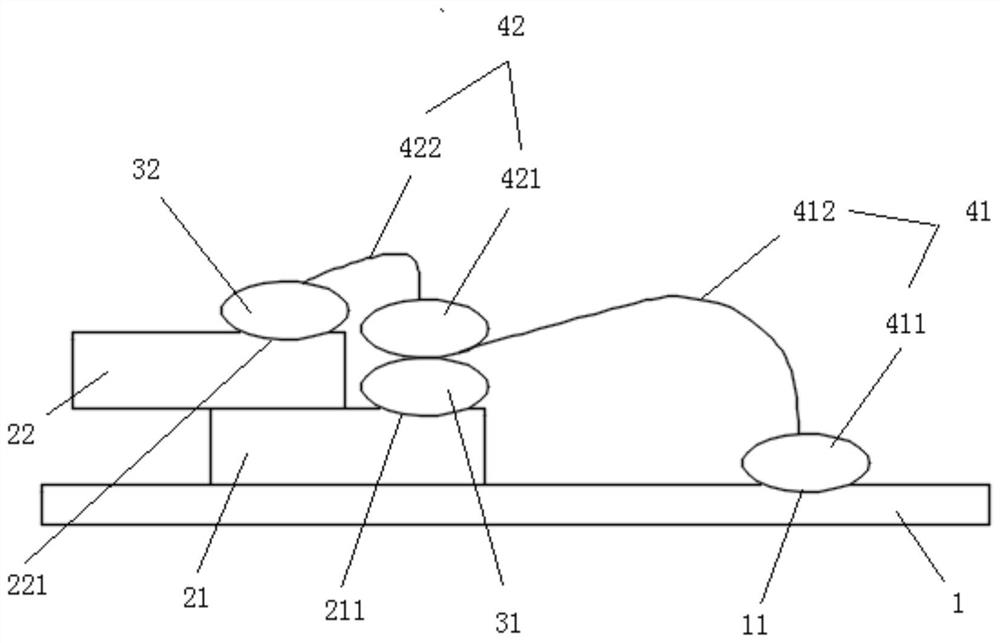

[0055] optional, such as image 3 , Figure 4 As shown, the chip bonding structure of this embodiment realizes the electrical connection between multiple chips and the substrate. In this embodiment, it also includes: a second chip 22 , a second gold pad 32 and a second copper connection wire 42 .

[0056] The second chip 22 is dislocated and stacked on the first chip 21 , a step is formed between the second chip 22 and the first chip 21 , and the first gold pad 31 on the first chip 21 is set at the step.

[0057] The second gold pad 32 is disposed at one end of the second chip 22 , and the second gold pad 32 is located at one end close to the first gold pad 31 .

[0058] The second copper connection line 42 includes: a second copper welding point 421 and a second copper welding line 422 .

[0059] The second copper pad 421 of the second copper connection wire 42 is located at one end of the second copper pad 422, and the second copper pad 421 and the other end of the second ...

Embodiment 3

[0068] This embodiment provides a welding method for realizing a chip welding structure, including the following steps:

[0069] S1. Use a wire bonding machine to respectively weld first gold pads and second gold pads on the first chip and the second chip with gold wires.

[0070] S2. Using a wire bonding machine, copper wires are used to electrically connect the second gold soldering point to the first gold soldering point, and to electrically connect the first gold soldering point to the substrate.

[0071] Specifically, when the chip is connected to the substrate, use a wire bonding machine to first use gold wires to weld gold solder joints on the chip respectively, and if it is a multi-layer chip stacked in a multi-layer dislocation, solder the chips on each layer separately. Gold solder joints.

[0072] Then copper wires are used to connect the gold pads on the chips of each layer to the substrate in sequence. When connecting copper wires, if the space permits, use the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More