Vortex light coding all-optical logic gate based on binary phase shift keying, and implementation method thereof

A technology of binary phase shift keying and implementation method, applied in the direction of logic circuits using optoelectronic devices, logic circuits using specific components, logic circuits, etc., which can solve unfavorable cascade design, weak anti-interference ability, and inconsistent output intensity. and other problems, to achieve good anti-interference ability and easy integration.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

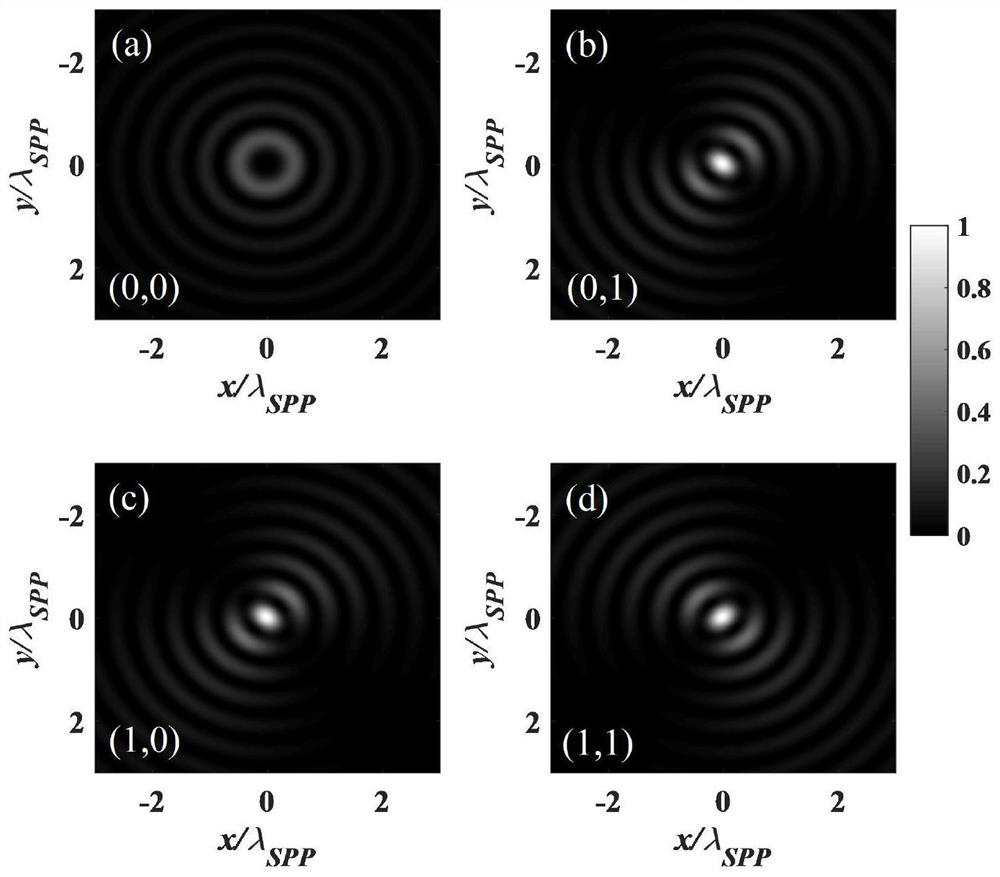

[0028] Embodiment 1: OR logic gate.

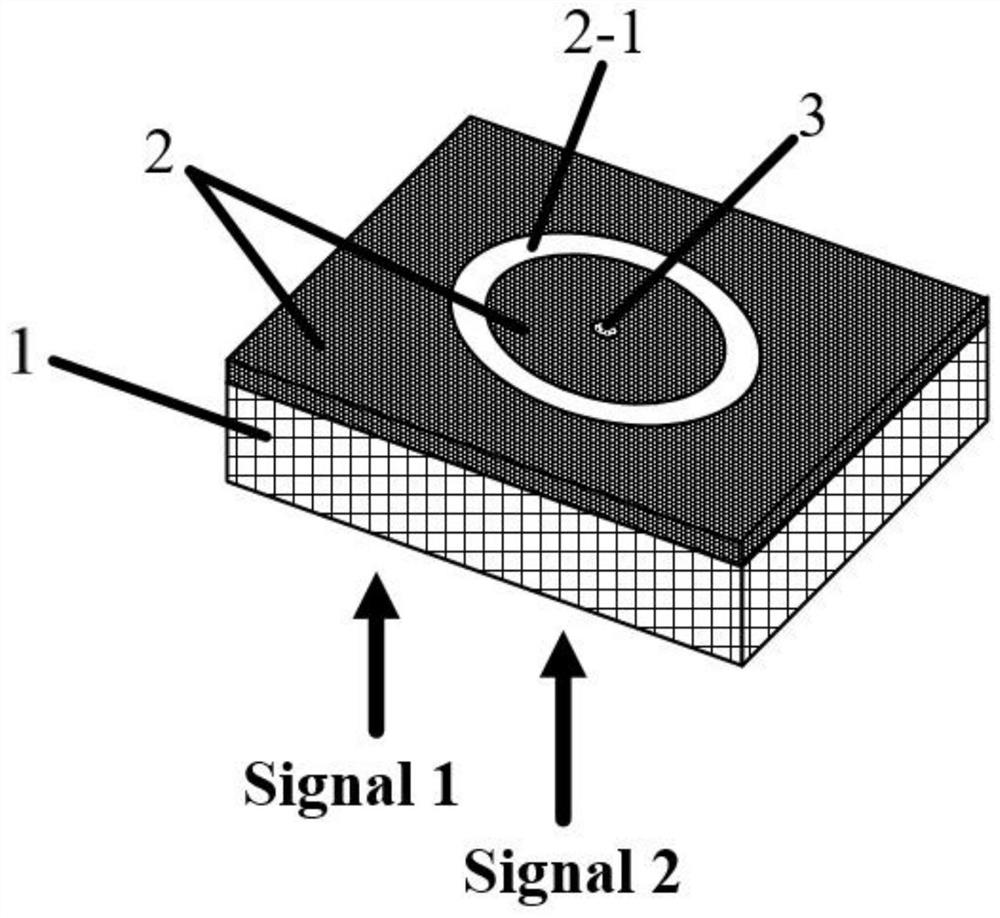

[0029] Such as figure 1 As shown, the vortex optically encoded OR gate in this embodiment includes input signals Signal 1 and Signal 2 , a substrate 1 , a nanometal film 2 , an annular nanogroove 2 - 1 and an output port 3 . The vortex light is vertically incident on the lower surface of the substrate 1, and excites the SPPs at the annular nano-groove 2-1 on the nano-metal film 2. The SPPs transport along the surface of the nanometal film 2 and converge at the output port 3 . Different intensity values of SPPs at the output port 3 are respectively defined as different output logic states. For an ideal OR gate, when the input logic state (A, B) is (0, 0), the SPPs intensity at the output port 3 needs to be 0 to represent the output logic state "0"; when the input logic state (A, B) When (0, 1), (1, 0) and (1, 1), the intensity of SPPs at the output port 3 should be a uniform non-zero value to represent the output logic state "1". Sinc...

Embodiment 2

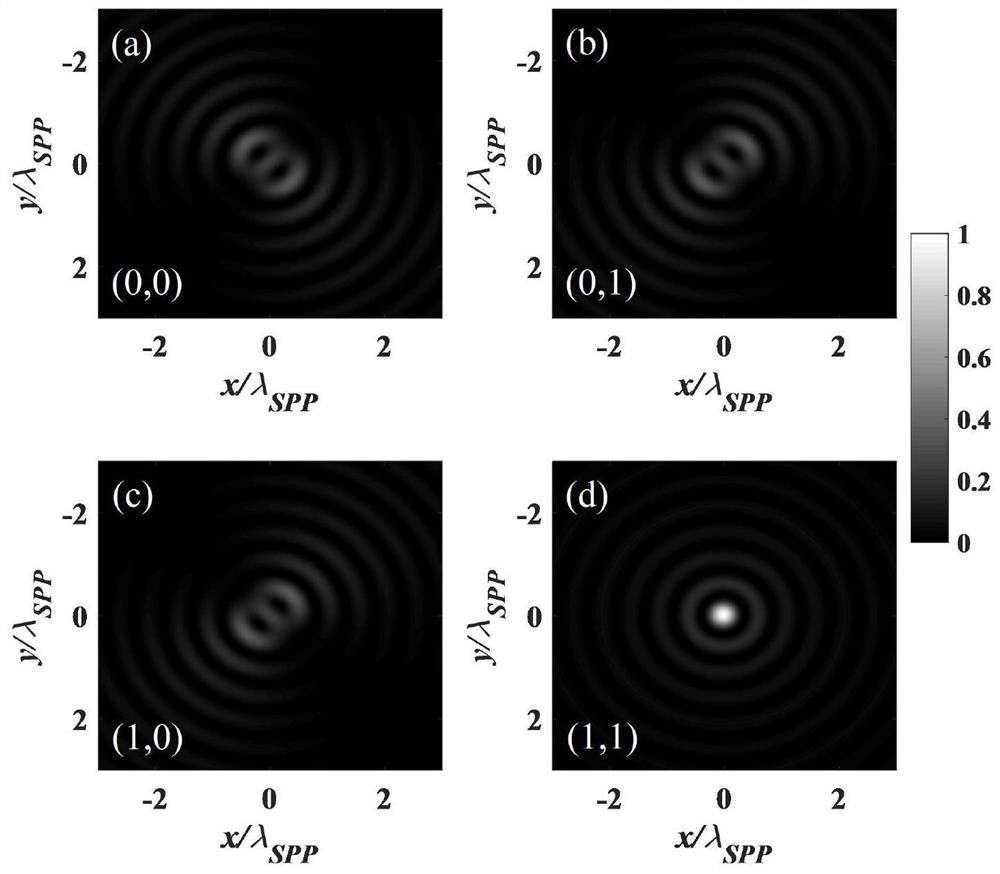

[0030] Embodiment 2: AND logic gate.

[0031] Such as figure 1 As shown, the AND gate of the vortex optical encoding in this embodiment includes input signals Signal 1 and Signal 2 , a substrate 1 , a nanometal film 2 , an annular nanogroove 2 - 1 and an output port 3 . The vortex light is vertically incident on the lower surface of the substrate 1, and excites the SPPs at the annular nano-groove 2-1 on the nano-metal film 2. The SPPs transport along the surface of the nanometal film 2 and converge at the output port 3 . Different intensity values of SPPs at the output port 3 are respectively defined as different output logic states. For an ideal AND gate, when the input logic states (A,B) are (0, 0), (0, 1) and (1, 0), the intensity of SPPs at the output port 3 is 0, representing the output logic state "0 "; when the input logic state (A, B) is (1, 1), the intensity of SPPs at the output port 3 is a value other than 0, representing the output logic state "1". Since the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More