Method for etching cantilever beam on CSOI

A cantilever beam and insulating layer technology, which is applied in the field of semiconductor manufacturing technology, can solve the problems of device yield reduction, upper surface layer depression, etch damage, and achieve the effect of improving yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

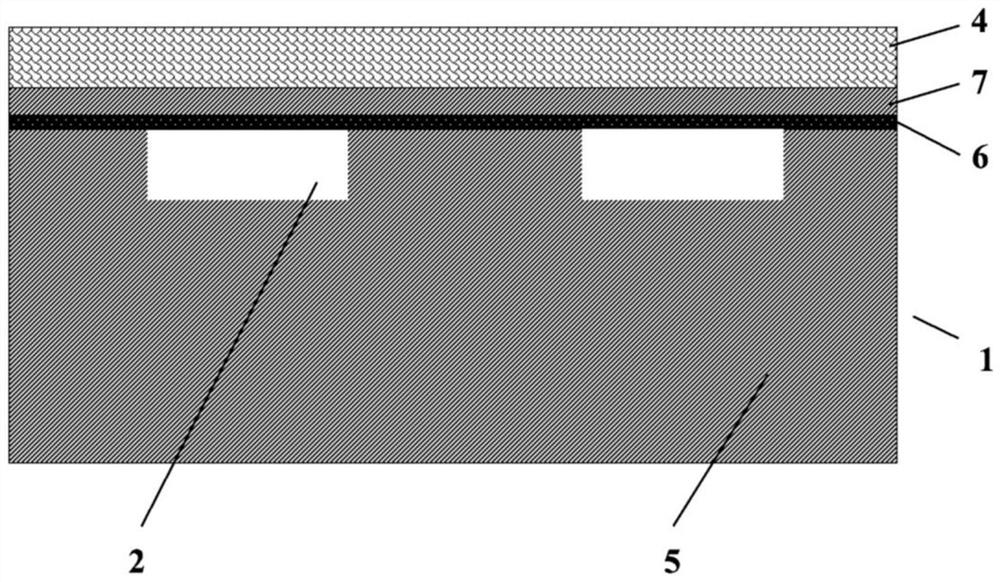

[0033]Such asFigure 1-5 As shown, a method for etching a cantilever beam on CSOI includes the following steps:

[0034]Step 1: Provide a set of silicon wafers as the first insulating layer 5, and fabricate a cavity 2 structure on the surface of the first insulating layer 5;

[0035]Step 2: Bonding a composite layer composed of a transition layer 6 and a second insulating layer 7 on the surface of the first insulating layer 5 to form a wafer substrate 1 together;

[0036]Step 3: Depositing materials sequentially on the surface of the composite layer to form the structural layer 4;

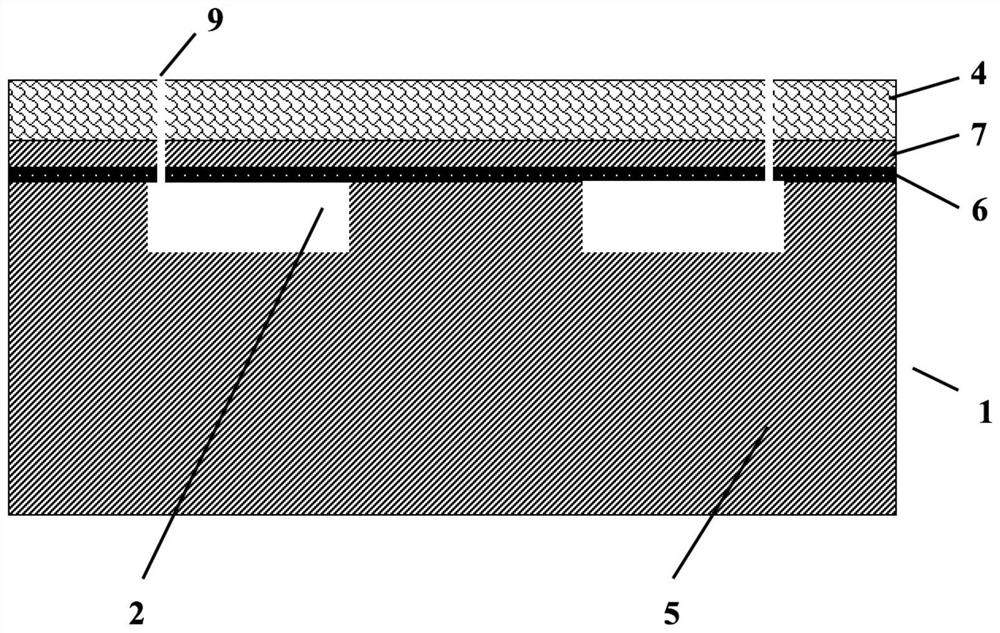

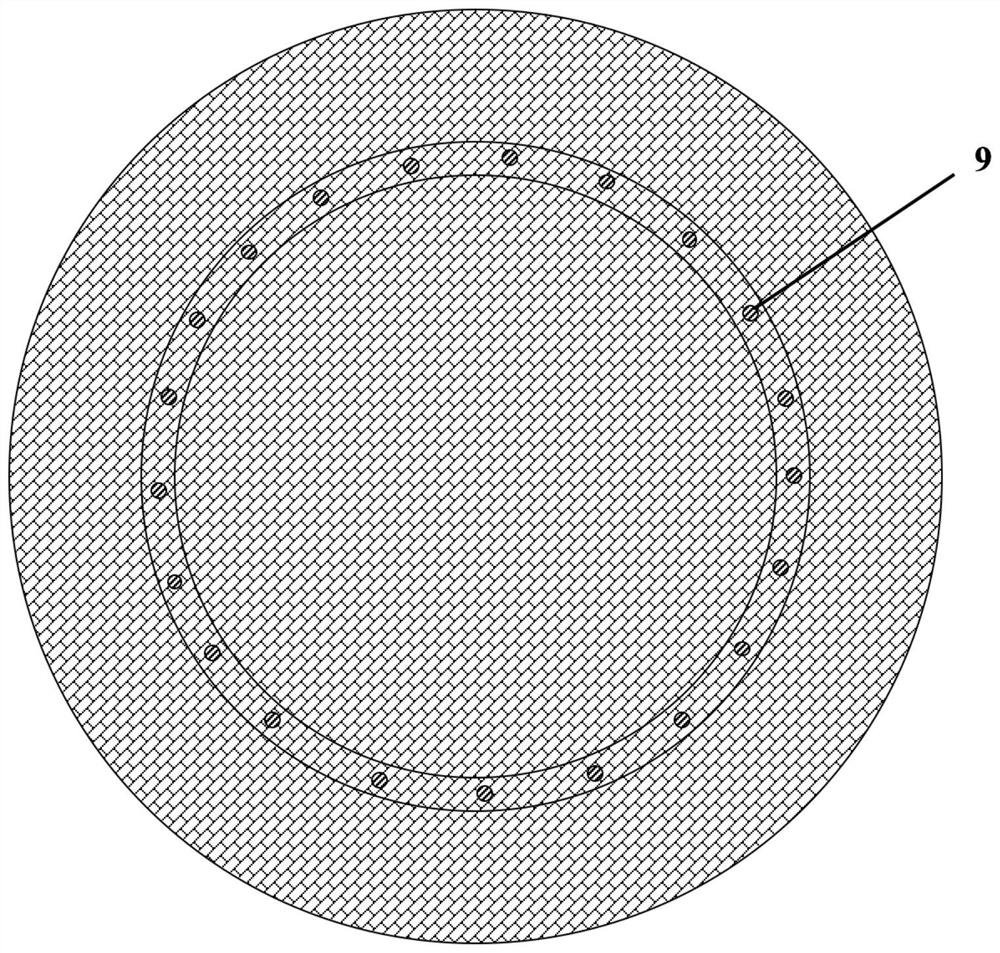

[0037]Step 4: Etch the structure layer 4, the second insulating layer 7 and the transition layer 6 anywhere within the target etching area 3 from top to bottom to form a plurality of vent holes 9 so that the outside world is connected to the cavity 2;

[0038]Step 5: Perform pattern etching on the original target etching area 3, and finally form a target structure.

[0039]In other embodiments, the first insulating layer 5...

Embodiment 2

[0044]Such asFigure 1-6As shown, the difference between this embodiment and Embodiment 1 lies in:

[0045]The step 1 further includes the following operations: filling the cavity 2 with silicon dioxide 8 to keep the surface of the first insulating layer 5 even.

[0046]The silicon substrate surface of the first insulating layer 5 is flattened by pre-embedded silicon dioxide 8, and after bonding the composite layer, a flat first insulating layer 5 / transition layer 6 / second insulating layer 7 substrate is formed, which is next to the flat The material is deposited uniformly on the surface of the structure layer 4 to maintain the flatness, and the actual processed device can restore the ideal situation to the greatest extent. The embedded silicon dioxide 8 is released during etching.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More