A parameter optimization design method for sic MOSFET drive circuit

A technology for optimizing design and driving circuits, applied in CAD circuit design, design optimization/simulation, special data processing applications, etc., can solve problems such as incomplete optimization design method of SiC MOSFET driving circuit parameters, and unconsidered key stray parameters of SiC MOSFET, etc. Achieve the effects of improving design reliability, saving design time, and improving design efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] An embodiment of the present invention:

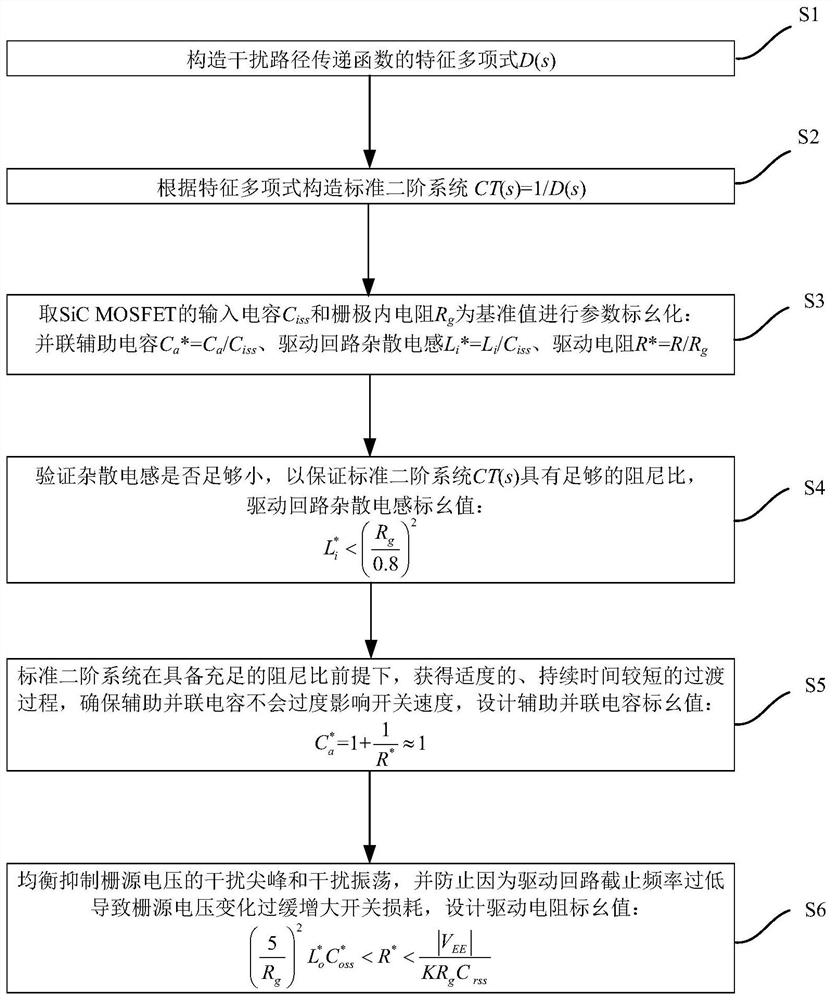

[0057] Such as figure 1 As shown, the method includes the following steps:

[0058] Step S1: Construct the characteristic polynomial D(s) of the interference path transfer function;

[0059] Step S2: Construct a standard second-order system CT(s)=1 / D(s) according to the characteristic polynomial;

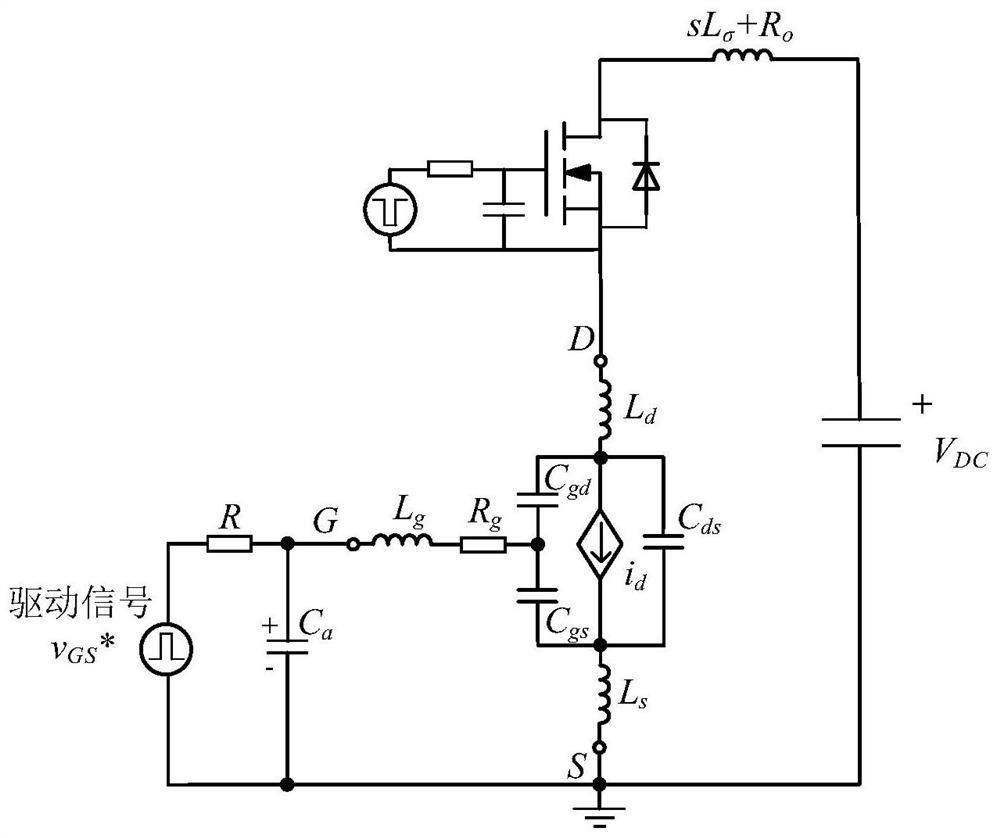

[0060] Step S3: Take the input capacitance C of the SiC MOSFET iss and gate internal resistance R g Parametric Unitization for Reference Values: Parallel Auxiliary Capacitor Drive circuit stray inductance Drive resistor R * =R / R g ;

[0061] Step S4: Verify whether the stray inductance is small enough to ensure that the standard second-order system CT(s) has a sufficient damping ratio, and the per unit value of the stray inductance of the drive circuit is:

[0062]

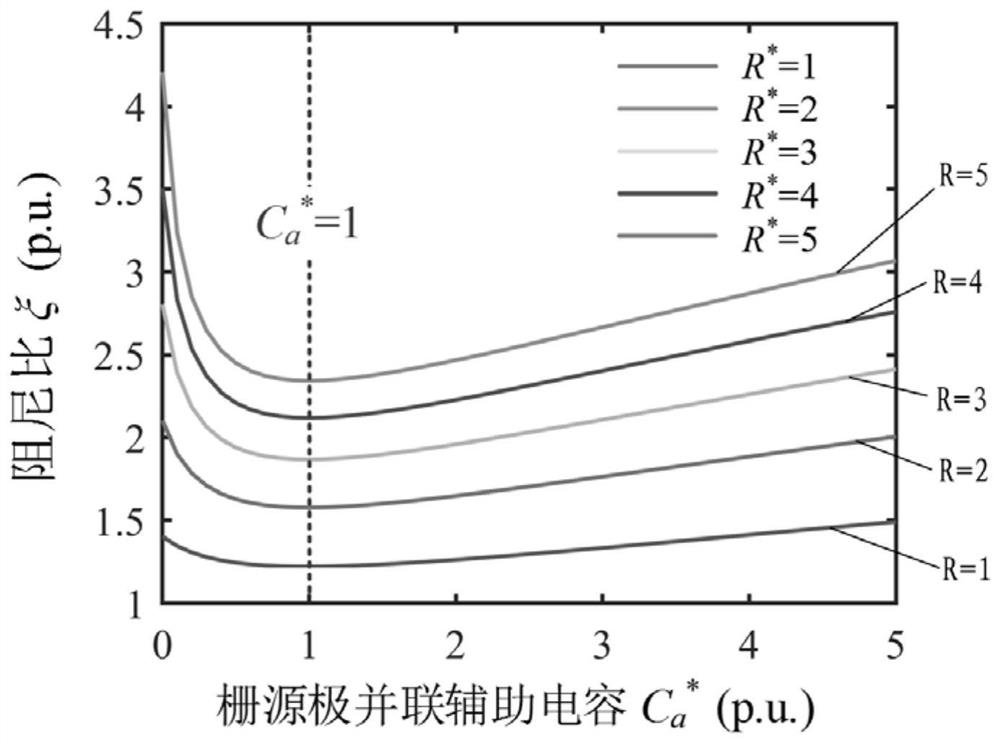

[0063] Step S5: Under the premise of sufficient damping ratio, the standard second-order system obtains a moderate transition process with a short duration ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More