Clock delay detection method and device, clock delay compensation method and device, terminal and readable storage medium

A clock delay and detection method technology, applied in the field of communication, can solve problems such as large errors, inconsistent impedance matching, and inability to use

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

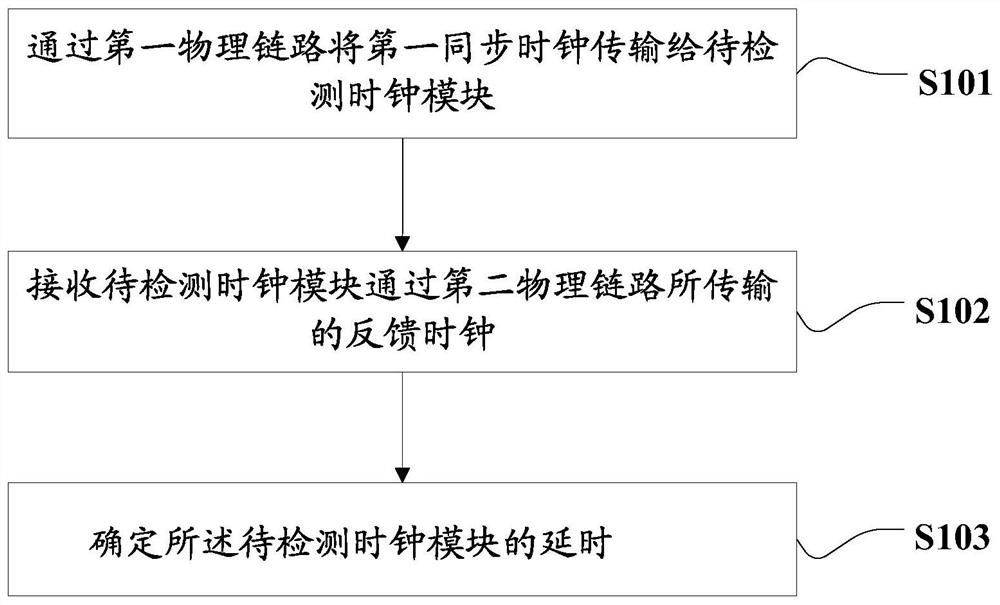

[0052] See figure 1 , a clock delay detection method provided in this embodiment includes:

[0053] S101: Transmit the first synchronous clock to the clock module to be detected through the first physical link;

[0054] S102: Receive the feedback clock transmitted by the clock module to be detected through the second physical link;

[0055] S103: Determine the delay of the clock module to be detected.

[0056] In some embodiments, the clock delay detection method in the embodiment of the present invention is applied to a switch device, and the switch device includes but is not limited to: a main clock module, a transmission link, a clock module to be detected, and a storage module;

[0057] Among them, the main clock module is the core clock module in the switch equipment, and its function can accept the synchronization of clock devices and equipment such as time server, GPS antenna, BITS clock, 1588 module, etc., and can also be synchronized with internal devices and equipm...

Embodiment 2

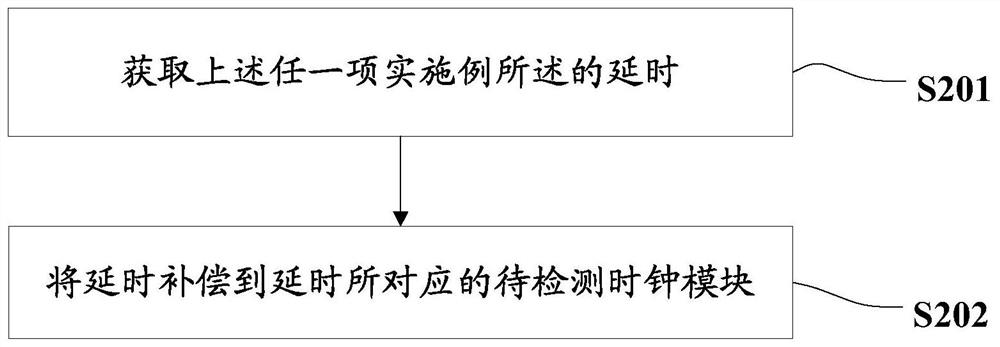

[0090] See figure 2 , a clock delay compensation method provided in this embodiment includes:

[0091] S201. Obtain the time delay described in any one of the above embodiments;

[0092] S202. Compensate the delay to the clock module to be detected corresponding to the delay.

[0093] It should be noted that the delay compensation to the clock module to be detected corresponding to the delay can be performed manually or automatically.

[0094] In some embodiments, the delay is compensated to the clock module to be detected corresponding to the delay, and the compensation methods include but are not limited to the following methods:

[0095] Compensate the delay to the constant delay memory of the clock module to be detected through the management interface, and the clock module to be detected will remove the delay during subsequent clock synchronization calculations;

[0096] or,

[0097] Modifying the phase of the second synchronous clock, so that the second synchronous ...

no. 3 example

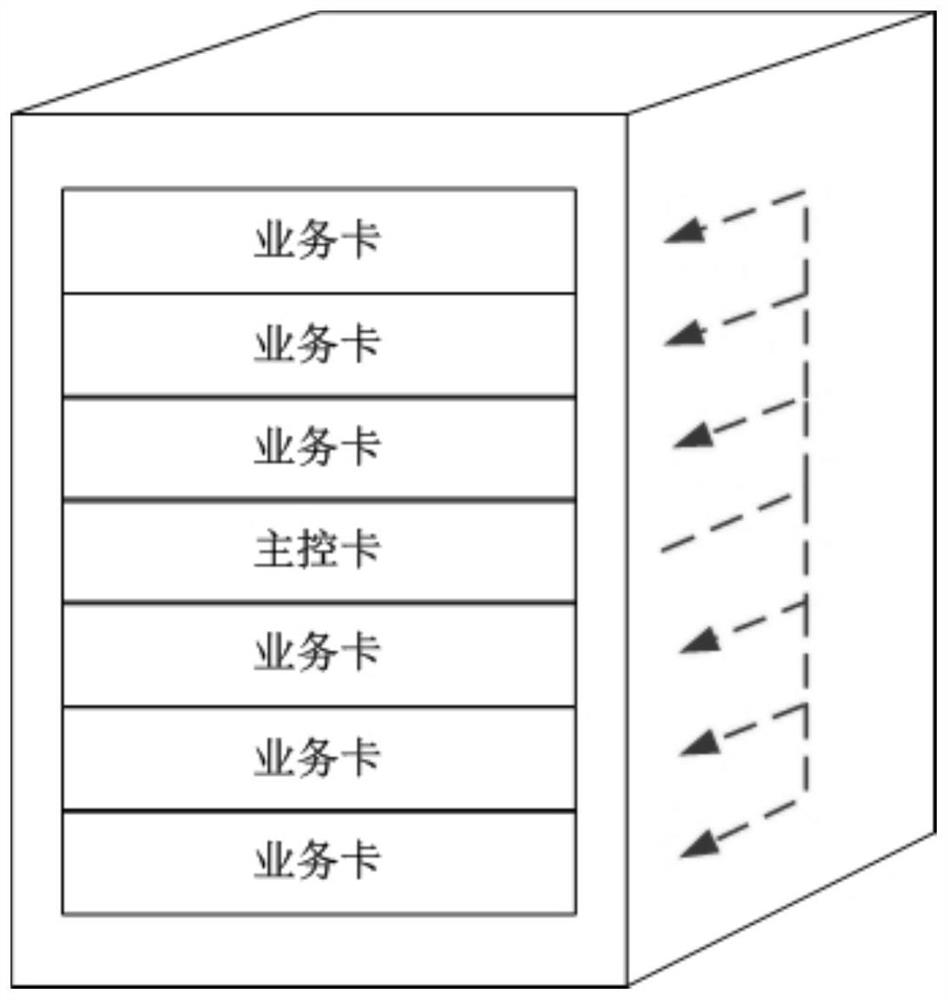

[0108] The method for detecting and compensating clock delays provided by the above embodiments will be specifically described below by taking an application scenario in which the method provided by the above embodiments is applied to a rack switch as an example.

[0109] It should be noted that the methods provided by the present invention are not limited to being applied to rack switches, and the following is only an exemplary description. Other switch devices that use physical links to transmit synchronous clocks are also applicable to the method provided by the present invention.

[0110] see image 3 , image 3 It is a schematic diagram of the topology of a rack-mounted switch. The switch is composed of a main control card and multiple service cards.

[0111] see Figure 4 , Figure 4 It is a topological schematic diagram of clock delay detection and compensation, and the device includes a main clock module, a clock module to be detected, a storage module, a first ph...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More