Semiconductor structure and forming method thereof

A semiconductor and patterning technology, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of different etching load effects, pattern bridging, pattern transfer distortion, etc., to reduce the etching load effect, Uniform appearance and accurate size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] Specific implementations of the semiconductor structure and its forming method provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

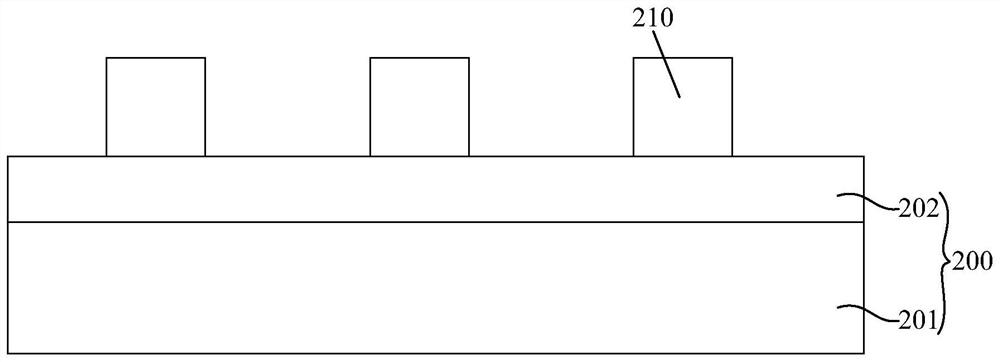

[0027] Please refer to figure 2 , providing a substrate 200, and forming a patterned sacrificial layer 210 on the surface of the substrate 200.

[0028] In this specific embodiment, the base 200 includes a substrate 201 and a target layer 202 on the surface of the substrate 201 .

[0029] The material of the substrate 201 is semiconductor materials such as silicon, germanium, silicon germanium, silicon carbide or indium gallium; the substrate 201 can also be a silicon-on-insulator substrate, a germanium-on-insulator substrate or an on-insulator substrate. silicon germanium substrate. In this specific embodiment, the substrate 201 is a single crystal silicon substrate.

[0030] Semiconductor devices such as MOS transistors, resistors, capacitors or inductors may also be form...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More