SGTMOSFET device and manufacturing method

A technology of devices and conditions, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as ugly appearance and influence on device reliability, so as to reduce the influence of warpage, improve product yield, and reduce stress Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

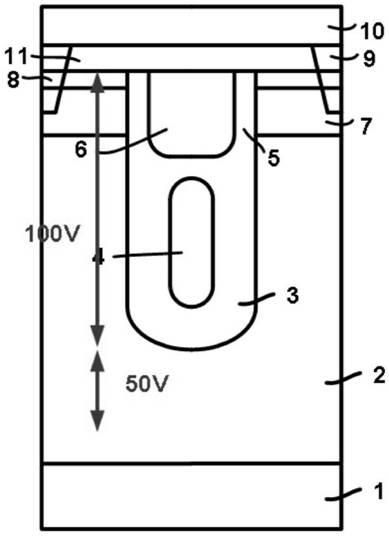

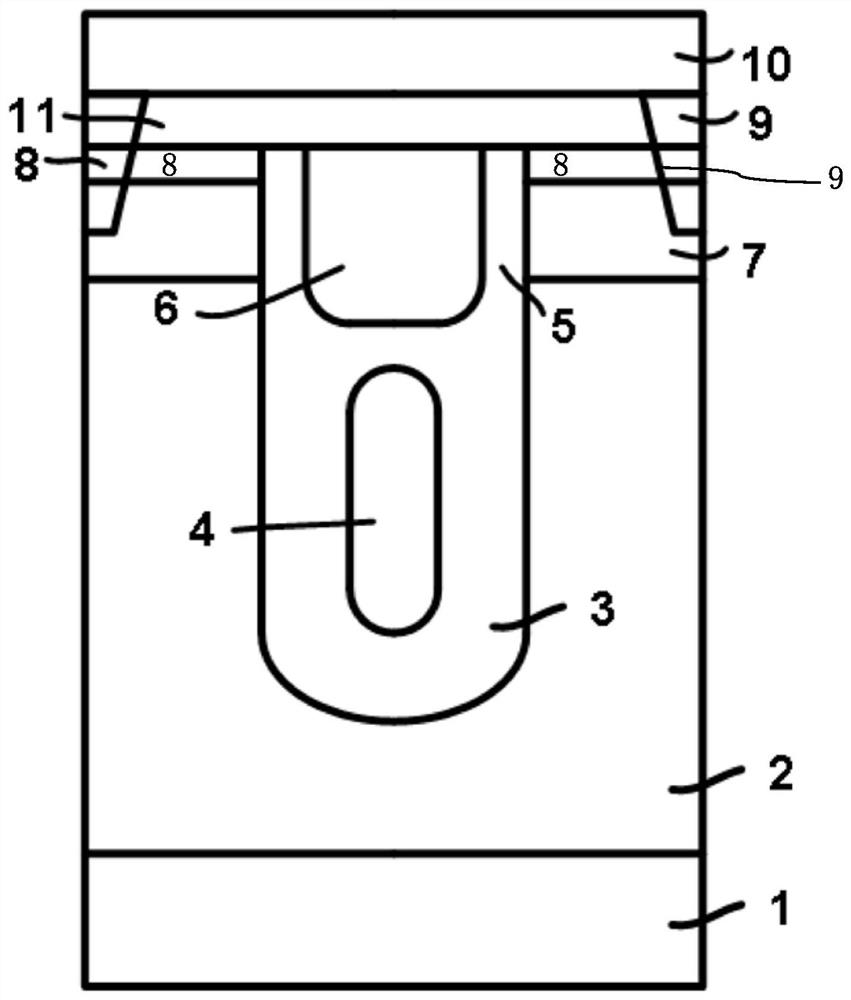

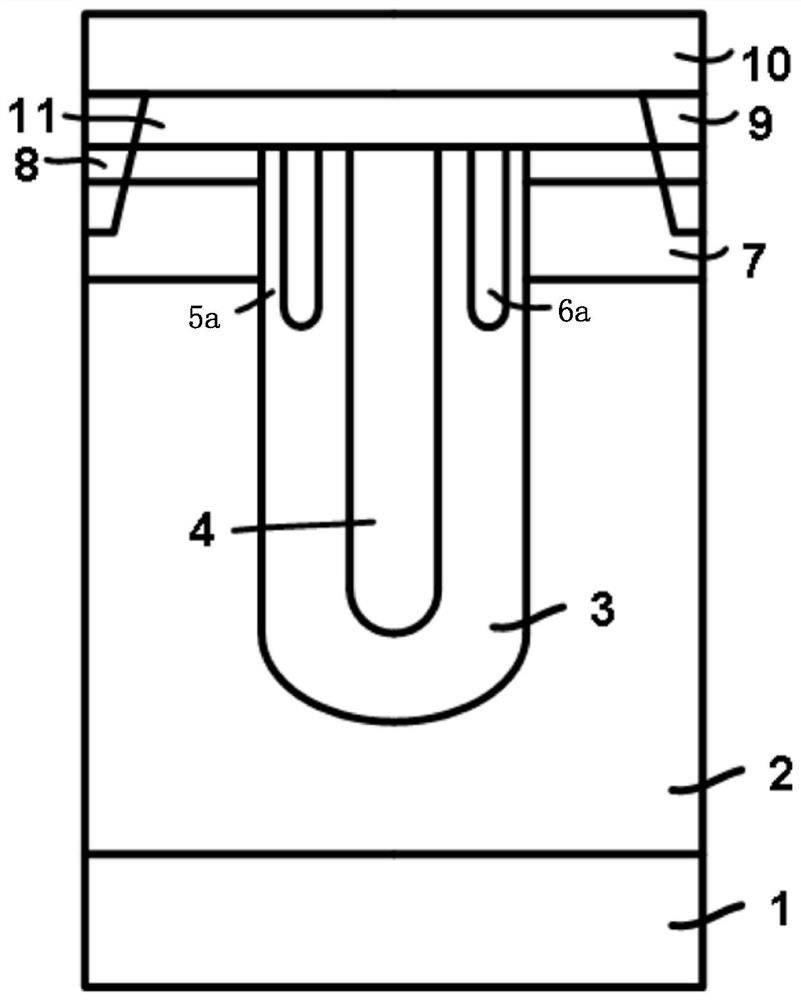

[0090] Such as Figure 5 Shown is a schematic structural diagram of the SGTMOSFET device of the embodiment of the present invention; the withstand voltage of the SGTMOSFET device of the embodiment of the present invention is above 150V. A gate structure is formed in the gate trench.

[0091] The gate trench is formed in the first epitaxial layer 2 of the first conductivity type. The first epitaxial layer 2 is formed on the heavily doped semiconductor substrate 1 of the first conductivity type.

[0092] A bottom oxide layer 3 is formed on the inner surface of the gate trench. The thickness of the bottom oxide layer 3 is required to meet the withstand voltage condition of 150V or more. The thicker the bottom oxide layer 3 is, the lower the bottom oxide layer is. 3 has a higher withstand voltage; the bottom oxide layer 3 is composed of a thermal oxide layer and a CVD-deposited oxide layer, so as to meet the stress condition of the bottom oxide layer 3 .

[0093] The bottom oxi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More