Packaging structure and preparation method thereof

A technology of packaging structure and rewiring structure, which is applied in the fields of semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc. The effect of increasing the integration density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

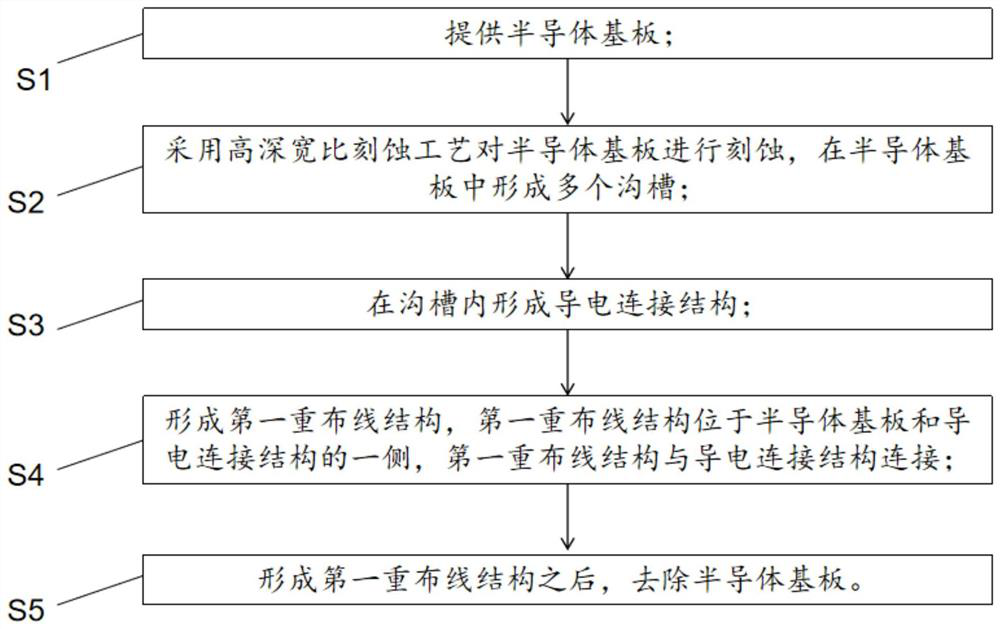

[0043] On this basis, the present invention provides a method for preparing a packaging structure, comprising the following steps: providing a semiconductor substrate; etching the semiconductor substrate by using a high aspect ratio etching process, and forming a plurality of grooves in the semiconductor substrate groove; forming a conductive connection structure in the groove; forming a first rewiring structure, the first rewiring structure is located on one side of the semiconductor substrate and the conductive connection structure, and the first rewiring structure is connected to the conductive connection structure The conductive connection structure is connected; after the first rewiring structure is formed, the semiconductor substrate is removed. The packaging structure obtained by the above preparation method can simultaneously have higher integration density and high-frequency transmission capability.

[0044] The technical solutions of the present invention will be cle...

Embodiment 1

[0047] see figure 1 , the invention provides a method for preparing a packaging structure, comprising the following steps:

[0048] S1, providing a semiconductor substrate 1;

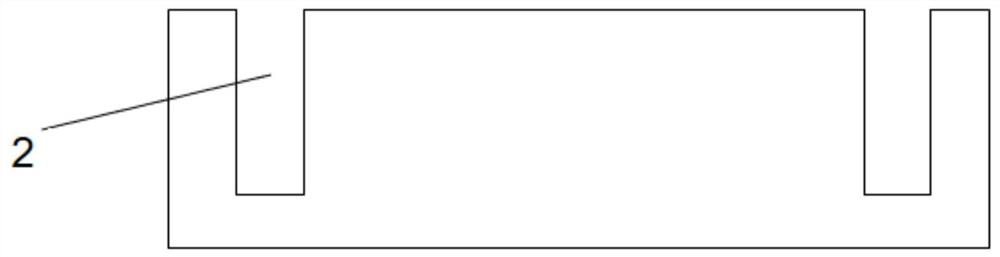

[0049] S2. Etching the semiconductor substrate 1 by using a high aspect ratio etching process to form a plurality of trenches 2 in the semiconductor substrate 1;

[0050] S3, forming a conductive connection structure 3 in the trench 2;

[0051] S4, forming a first rewiring structure 4, the first rewiring structure 4 is located on one side of the semiconductor substrate 1 and the conductive connection structure 3, the first rewiring structure 4 is connected to the conductive connection structure 3 connect;

[0052] S5. After the first rewiring structure 4 is formed, the semiconductor substrate 1 is removed.

[0053] In the preparation method of the above packaging structure, the semiconductor substrate is etched by a high aspect ratio etching process, a conductive connection structure is formed in th...

Embodiment 2

[0081] This embodiment provides a method for preparing a package structure, which differs from the method for preparing a package structure provided in Example 1 in that:

[0082] see Figure 16 , after the trench 2 is formed in step S2, a dielectric layer 12 is formed on the inner wall of the trench 2, so that after the conductive connection structure 3 is formed in step S3, as Figure 17 As shown, the dielectric layer 12 on the inner wall of the trench 2 is located between the conductive connection structure 3 and the semiconductor substrate 1, so that after the second encapsulation layer 9 is formed, as Figure 18 As shown, the second encapsulation layer 9 wraps the dielectric layer 12 outside the conductive connection structure 3 . Since the bonding force between the dielectric layer and the second encapsulation layer is greater than the bonding force between the conductive connection structure and the second encapsulation layer, the bonding stability of the second encaps...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More