Low quiescent current off-chip capacitor-free LDO with dynamically optimized power supply rejection ratio

A power supply rejection ratio and no off-chip capacitor technology, applied in the direction of high-efficiency power electronic conversion, regulation of electrical variables, control/regulation systems, etc., can solve the problems of high power consumption, large area, complex structure, etc., to achieve reduced area, The effect of reducing the area and improving the transient response performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be further described below in conjunction with accompanying drawing:

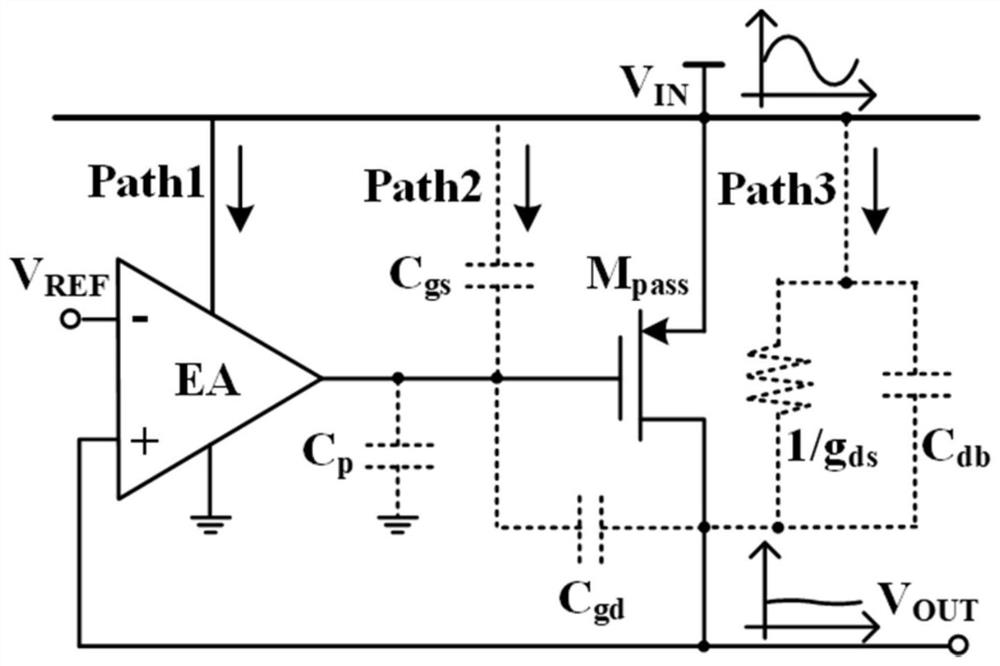

[0043] The analysis and optimization of PSR are carried out first. There are multiple paths between the power supply and the LDO output, allowing power supply noise to couple into the output, limiting PSR. figure 1 In the schematic diagram of , there are three main noise coupling paths: (1) error amplifier (EA, ErrorAmplifier); (2) power transistor gate-source parasitic capacitance (C gs ); (3) The drain body parasitic capacitance of the power tube (C db ) and drain-source conductance (g ds ). The power supply noise of the first two paths is first coupled to the M pass gate, then M pass Transconductance (g m ) is amplified and converted into a noise current.

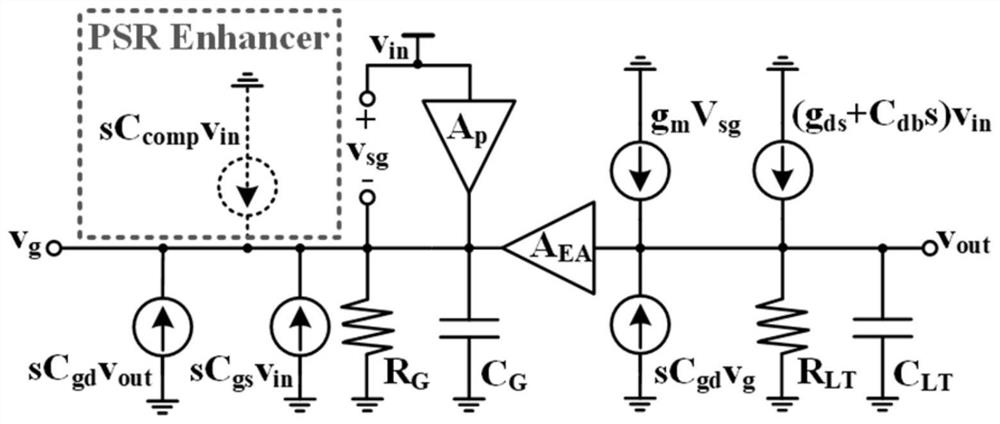

[0044] exist figure 2 In the small-signal model of , the parasitic capacitance is split into two ground-dividing capacitances and two voltage-controlled current sources. To optimize PSR, power supply noise c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More