An integrated radiation-resistant high-voltage soi device and its manufacturing method

A manufacturing method and anti-radiation technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., to achieve the effects of increasing concentration, improving anti-single event latch-up ability, and reducing parallel resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

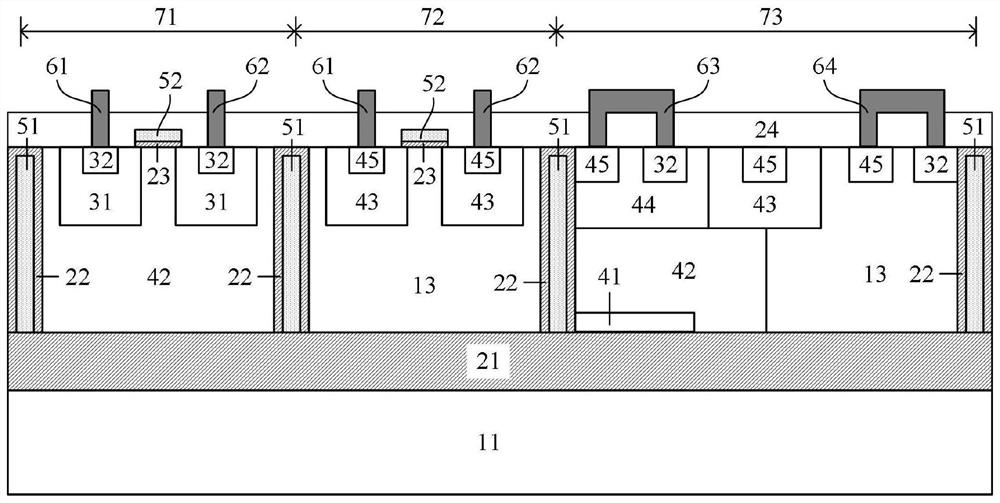

[0040] The invention provides an integrated radiation-resistant high-voltage SOI device, the structure of which is as follows figure 1 As shown, it includes a P-type substrate 11, a buried oxide layer 21, and an N-type epitaxial layer 13 formed in sequence; the surface of the N-type epitaxial layer 13 is provided with a high-voltage NMOS device 71, a high-voltage PMOS device 72, and a high-voltage ESD device 73; The integrated radiation-resistant high-voltage SOI device further includes an isolation oxide layer 22, a gate oxide layer 23, a pre-metal dielectric layer 24, a first P-type doped region 41, a second P-type doped region 42, and a third P-type doped region. 43. Fourth P-type doping region 44, fifth P-type doping region 45, first N-type doping region 31, second N-type doping region 32, polysilicon 51, polycrystalline gate electrode 52, source metal Electrode 61, drain metal electrode 62, anode metal electrode 63, cathode metal electrode 64; the first N-type doping regi...

Embodiment 2

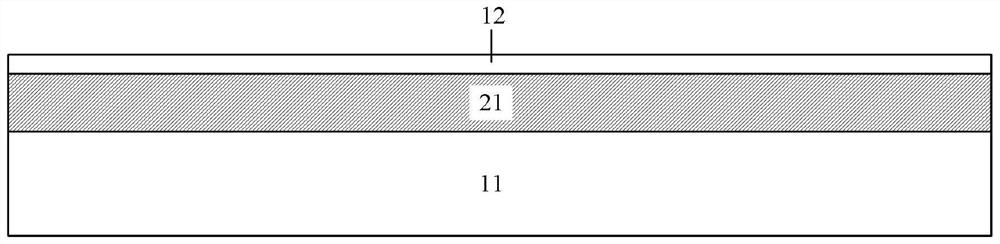

[0042] The invention also provides a manufacturing method of an integrated radiation-resistant high-voltage SOI device, which is fabricated on a silicon-on-insulator material, such as figure 2 As shown, the silicon-on-insulator has a P-type substrate 11, a buried oxide layer 21 and a top layer of silicon 12 stacked sequentially from bottom to top, including the following steps:

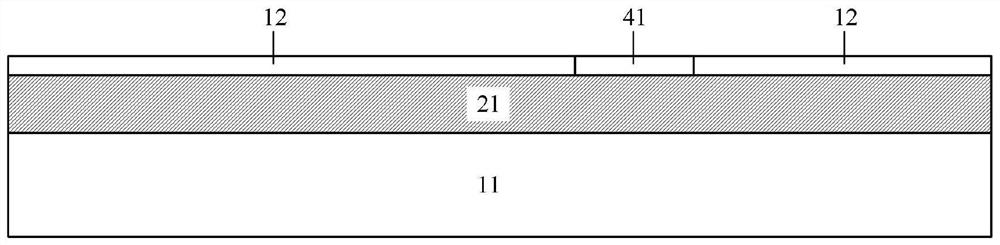

[0043] like image 3 As shown, an ion implantation process is used to implant P-type impurities on the top layer silicon 12 to form a first P-type doped region 41; the implantation dose of the first P-type doped region 41 is 1E13-1E15 cm -2 ;

[0044] like Figure 4 As shown, an N-type epitaxial layer 13 is formed on the buried oxide layer 21 by an epitaxial process; the N-type epitaxial layer 13 covers the first P-type doped region 41 ;

[0045] like Figure 5 As shown, the deep silicon trench is etched on the N-type epitaxial layer 13 by photolithography and etching process, and the isolation o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More