A phase-locked loop circuit and its control method, semiconductor device and electronic equipment

A phase-locked loop and circuit technology, applied in the direction of electrical components, automatic power control, etc., can solve problems such as system digital algorithm errors, delay chain abnormal duty cycle or glitches, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The following description is made to illustrate the general principles of the invention and is not meant to limit the inventive concepts claimed herein. Furthermore, certain features described herein can be used in combination with other described features in each of the various possible combinations and permutations.

[0020] Unless otherwise specifically defined herein, all terms are to be given their broadest interpretations, including meanings implied in this specification and meanings understood by those skilled in the art and / or as defined in dictionaries, treatises, and the like. In order to describe the technical content, structural features, achieved goals and effects of the present invention in detail, the following will be described in detail in conjunction with the embodiments and accompanying drawings.

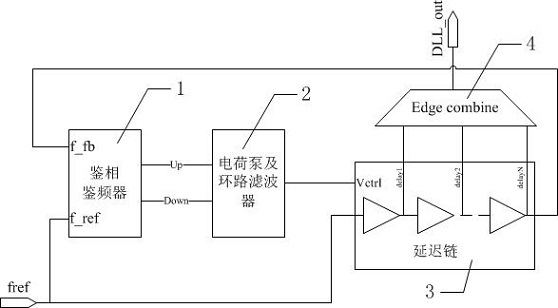

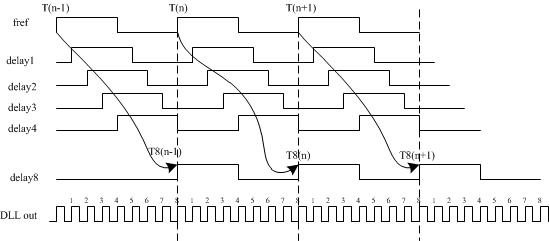

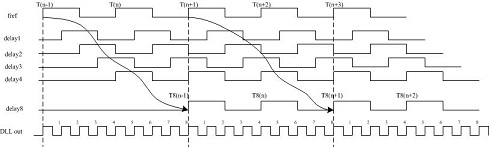

[0021] see figure 1 , figure 1 It is a circuit structure diagram of a delay-locked loop in the prior art, including a phase-frequency detector (or freque...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More