Array substrate structure, display device and preparation method of array substrate structure

一种阵列基板结构、金属层的技术,应用在电气元件、电固体器件、电路等方向,能够解决TFT器件可靠性难以保证、TFT器件存储电容降低、工艺复杂度提高等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

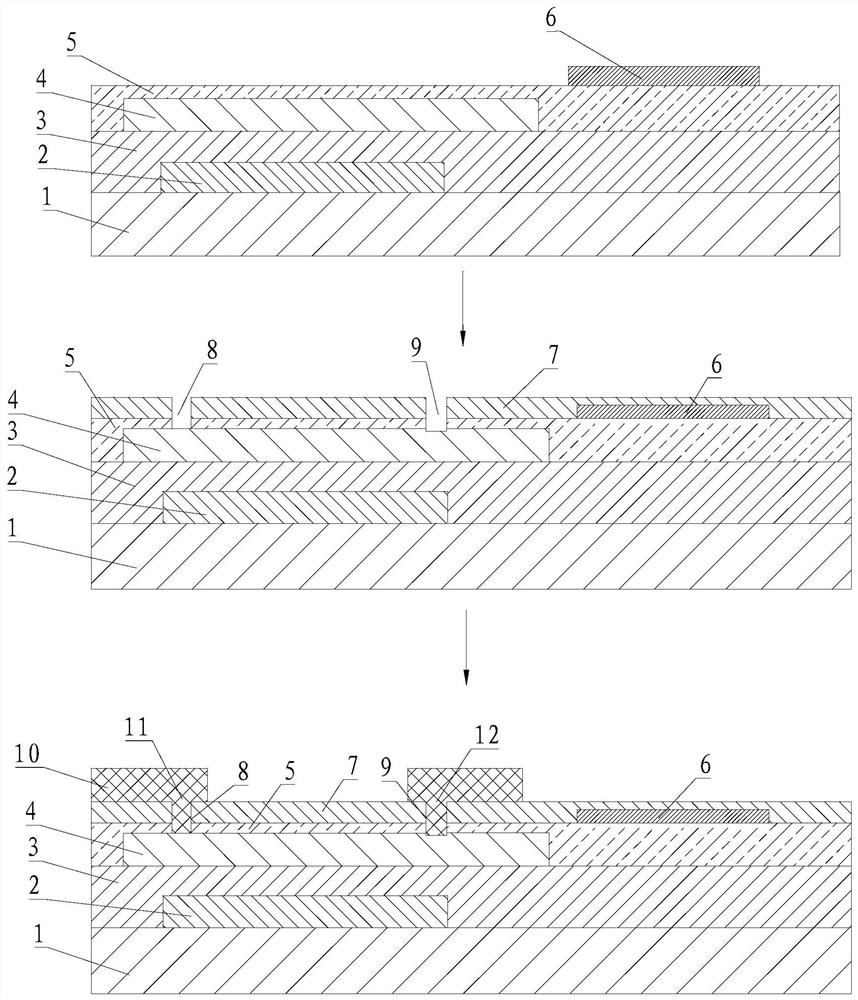

[0041] The present invention also provides a method for preparing a TFT array substrate, comprising the following steps:

[0042] Step 1: sequentially forming a gate, a gate insulating layer, an active layer and an etching barrier layer on the substrate, the gate being formed by a first metal layer;

[0043]Step 2: forming an auxiliary metal layer on the etching barrier layer;

[0044] Step 3: forming a passivation layer on the etching barrier layer and the auxiliary metal layer;

[0045] Step 4: Simultaneously pattern the passivation layer and the etching barrier layer through a patterning process to form a first via hole and a second via hole connected to the active layer;

[0046] Step 5: forming a third metal layer on the passivation layer, the third metal layer is connected to the active layer through the first via hole and the second via hole; A source electrode and a drain electrode are respectively formed at the first via hole and the second via hole.

[0047] Furth...

Embodiment 1

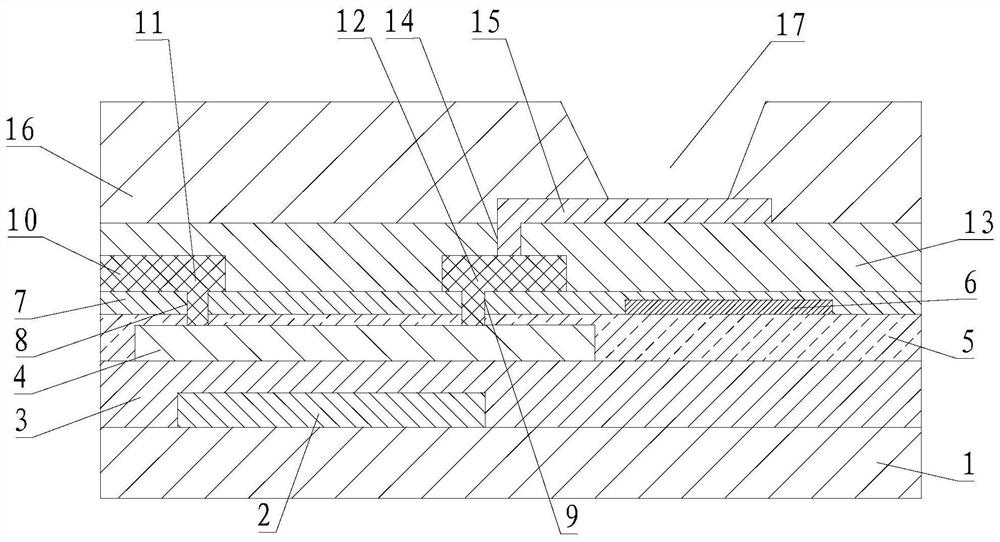

[0054] Please refer to figure 1 , Embodiment 1 of the present invention is:

[0055] A TFT array substrate, comprising a substrate 1, a gate formed by a first metal layer 2 disposed on the substrate 1, a gate insulating layer 3 disposed on the substrate 1 and the gate, and a gate insulating layer 3 disposed on the substrate 1. The active layer 4 on the gate insulating layer 3, the etching stopper layer 5 provided on the active layer 4 and the gate insulating layer 3, the auxiliary metal layer 6 provided on the etching stopper layer 5, The passivation layer 7 disposed on the etch barrier layer 5 and the auxiliary metal layer 6 passes through the passivation layer 7 and the etch barrier layer 5 and corresponds to the upper sides of the active layer 4 respectively. The first via hole 8 and the second via hole 9, the third metal layer 10 provided on the passivation layer 7, the third metal layer 10 passes through the first via hole 8 and the second via hole 9 respectively connec...

Embodiment 2

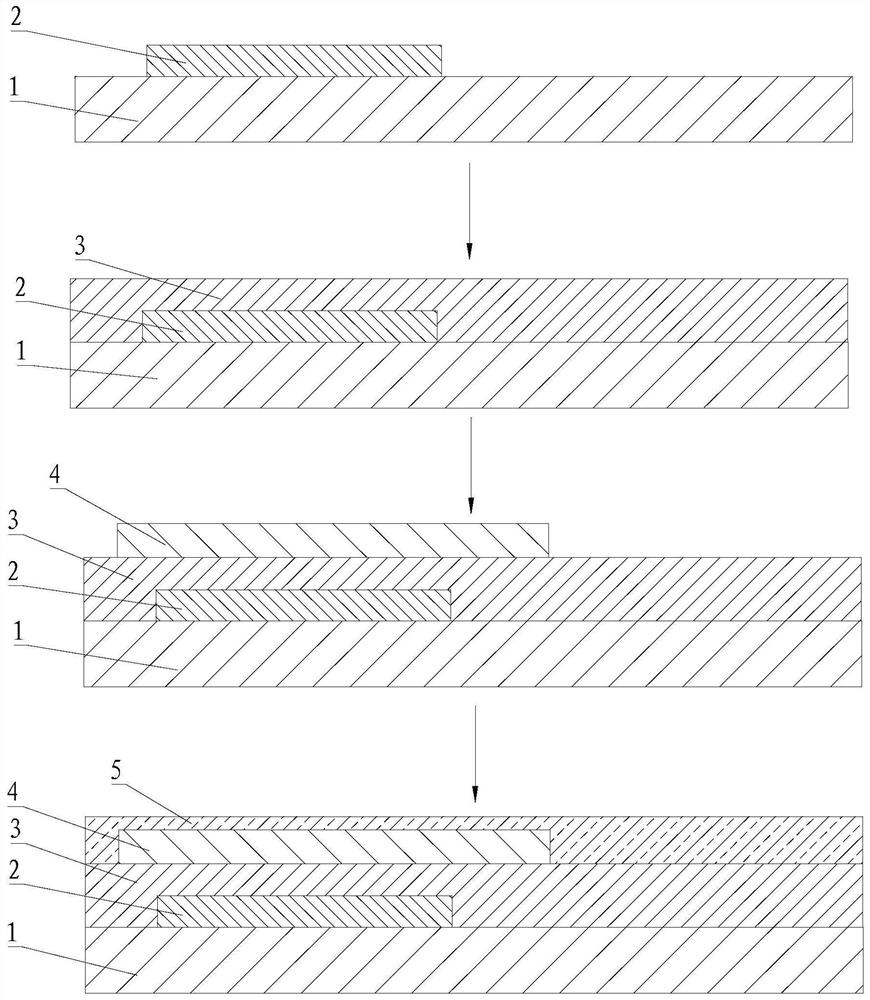

[0060] Please refer to Figure 2 to Figure 4 , the second embodiment of the present invention is:

[0061] A method for preparing a TFT array substrate, comprising the steps of:

[0062] Step 1: Evaporate the first metal layer (M1) 2 on the substrate 1 by physical vapor deposition (PVD), generally with a Mo / AL / Mo sandwich layer structure, and expose (photo) after photoresist coating, according to the mask Plate (MASK) design to form the required pattern, and then etch the first metal layer (M1) 2 to form the pattern of the gate (GE);

[0063] Step 2: Evaporating a gate insulating layer (GI) 3 on the substrate treated in step 1 by chemical vapor deposition (CVD);

[0064] Step 3: Evaporate an IGZO film on the substrate treated in step 2 by PVD method, and go through exposure (photo), etching (etch) and stripping (stripe) processes; finally form the required active layer (SE)4 picture of;

[0065] Step 4: Evaporating an etching stopper layer (ES) 5 on the substrate treated i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More