Method for manufacturing semiconductor integrated circuit

A technology for integrated circuits and manufacturing methods, applied in semiconductor/solid-state device manufacturing, semiconductor devices, circuits, etc., can solve the problems of semiconductor integrated circuit operating speed reduction, leakage current reduction, manufacturing difficulties, etc., to improve component separation characteristics, Effect of reducing leakage current and improving operating speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0109] The semiconductor integrated circuit according to Embodiment 1 of the present invention described below includes at least two elements and an isolation trench for isolating the elements, and SiOF which is a fluoride is filled in the isolation trench.

[0110] Here, the case where the effect of the invention is remarkable, that is, the case where the above-mentioned isolation trench is an STI formed on a silicon substrate, will be described.

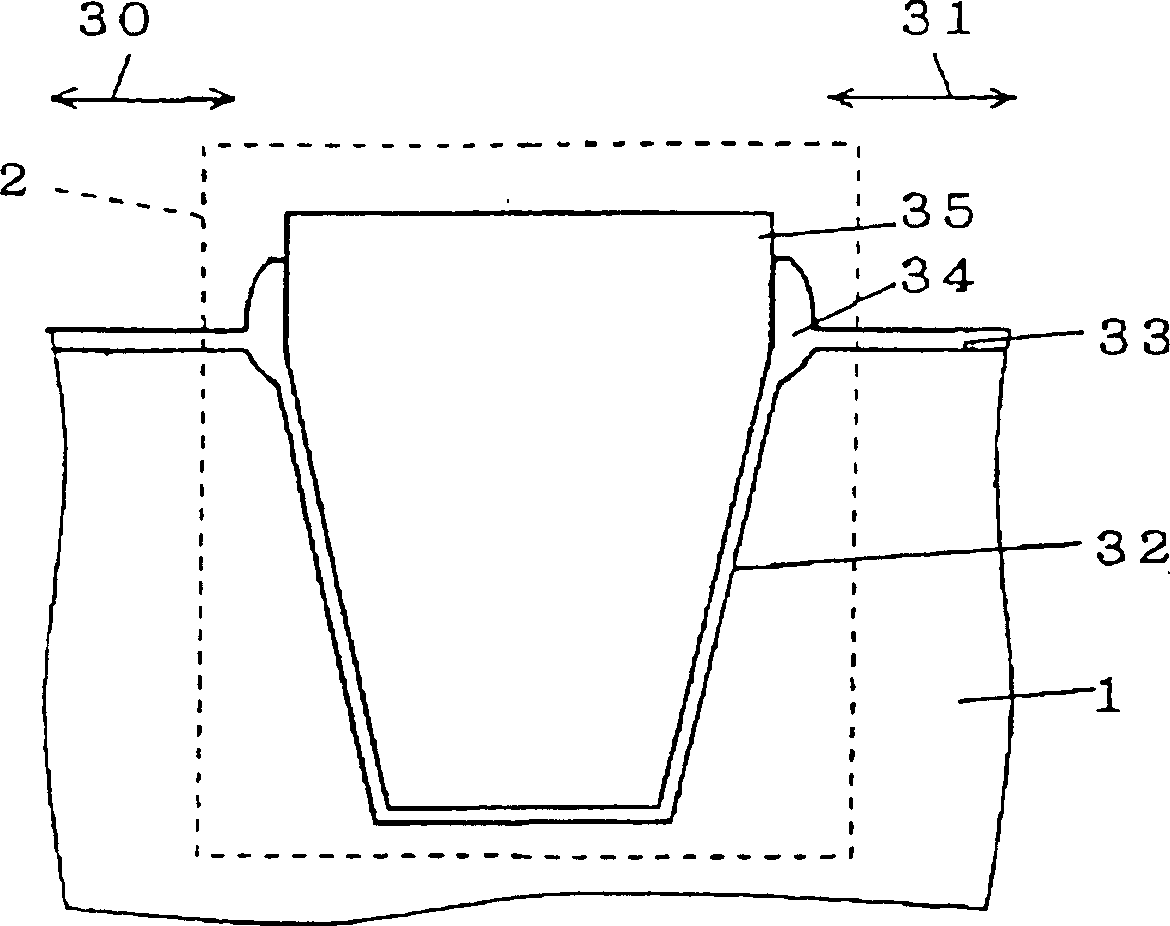

[0111] figure 1 It is a typical diagram showing an example of the structure of the semiconductor integrated circuit of the first embodiment. figure 1 An enlarged cross section of the vicinity of STI2 formed in the semiconductor integrated circuit is shown. In the semiconductor substrate 1, elements separated by STI2 are formed on active semiconductor regions indicated by arrows 30, 31.

[0112] STI2 is formed by silicon oxide film 32 formed on the side wall of the groove, silicon oxide 34 formed in the vicinity of the boundary ...

Embodiment 2

[0121] As described in Example 1, since the relative permittivity of SiOF filled with STI2 is higher than that of SiO 2 Small, so that the element separation characteristics can be improved. A substance with a very small relative permittivity is air, even in Figure 38 with Figure 39 In the conventional separation groove shown in , it is also described in the description of the prior art that the interior is made hollow.

[0122] However, the conventional method of manufacturing the isolation trenches with voids is complicated. The manufacturing method of the semiconductor integrated circuit according to the second embodiment simplifies the step of forming the cavity in the STI.

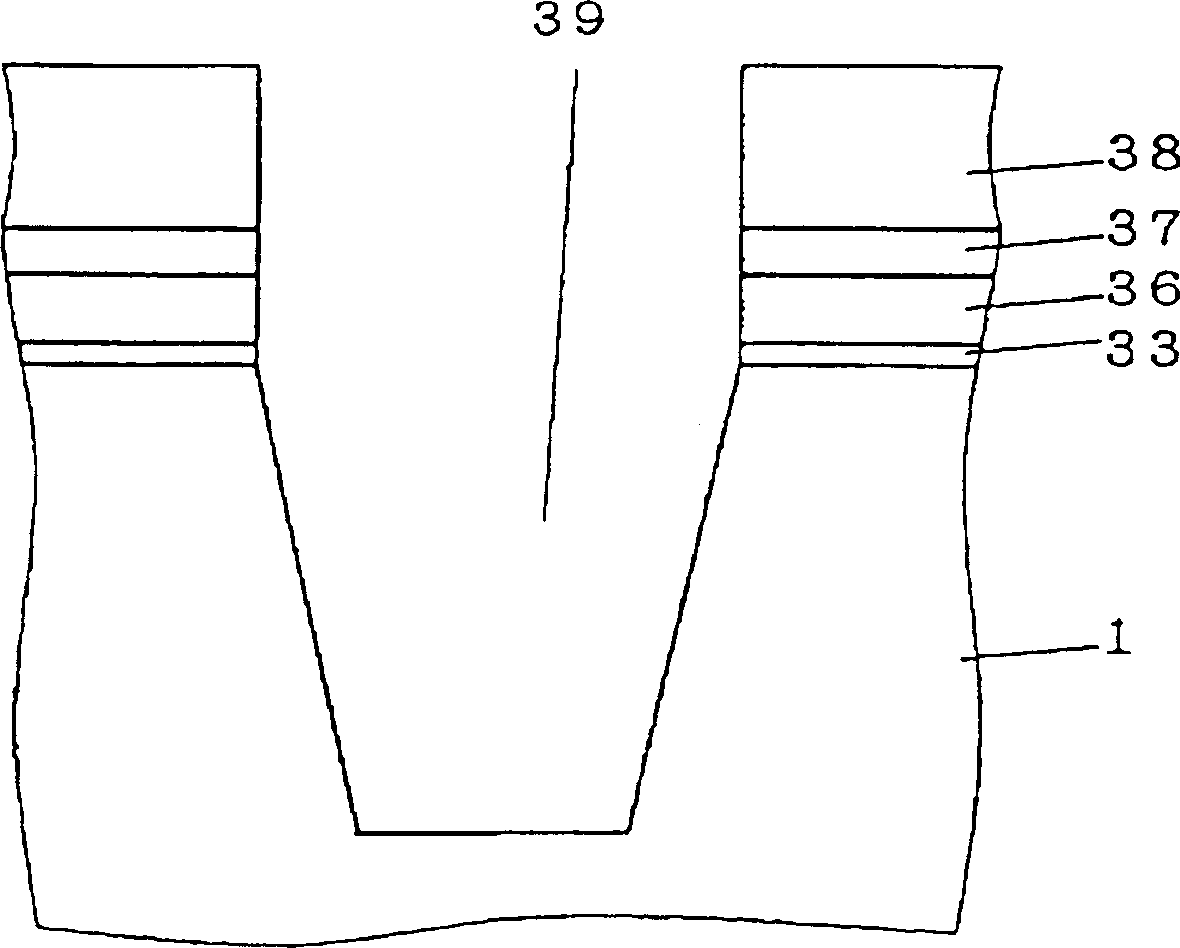

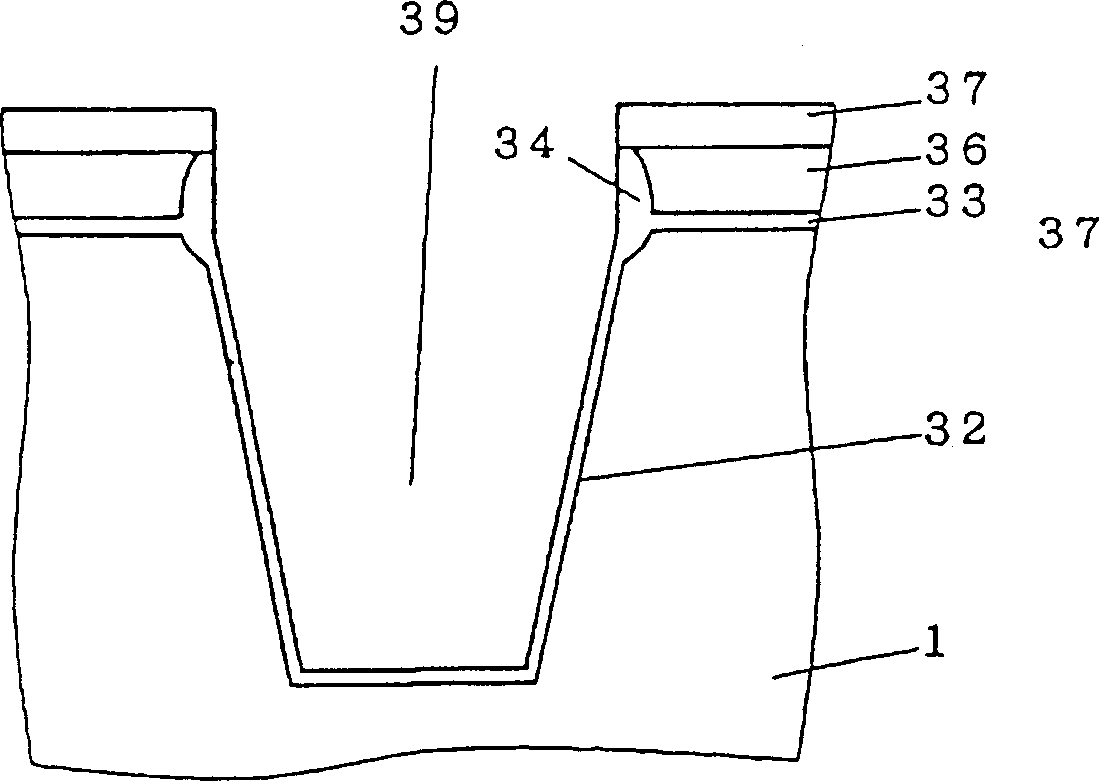

[0123] Figure 6 ~ Figure 11 It is a typical diagram showing each process of the manufacturing method of the semiconductor integrated circuit of the second embodiment. Figure 6 ~ Figure 11 used in the description of Example 1 Figure 1 to Figure 5 An enlarged cross section of the semiconducto...

Embodiment 3

[0133] The semiconductor integrated circuit of the third embodiment to be described next is characterized in that it forms a cavity under the wiring. Figure 12 It is a layout diagram showing the planar configuration of the semiconductor integrated circuit according to the third embodiment of the present invention. Figure 13 show Figure 12 The cross-section of the B-B line of the semiconductor integrated circuit, Figure 14 show Figure 12 C-C line cross section of a semiconductor integrated circuit.

[0134] exist Figure 12 In this case, a plurality of active semiconductor regions 50 are separated from each other by element isolation regions 51 . The active semiconductor region 50 also constitutes a MOS transistor while constituting the word line 52 laid thereon. will be Figure 12 The bit line 53 arranged perpendicularly to the word line 52 in the plane of , is connected to the source / drain region of the MOS transistor existing in the active semiconductor region 50 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More