Circuit time sequence optimization method based on register flexible time sequence library

An optimization method and register technology, applied in the direction of instruments, electrical digital data processing, special data processing applications, etc., to achieve the effect of improving circuit performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be further explained below in conjunction with the accompanying drawings.

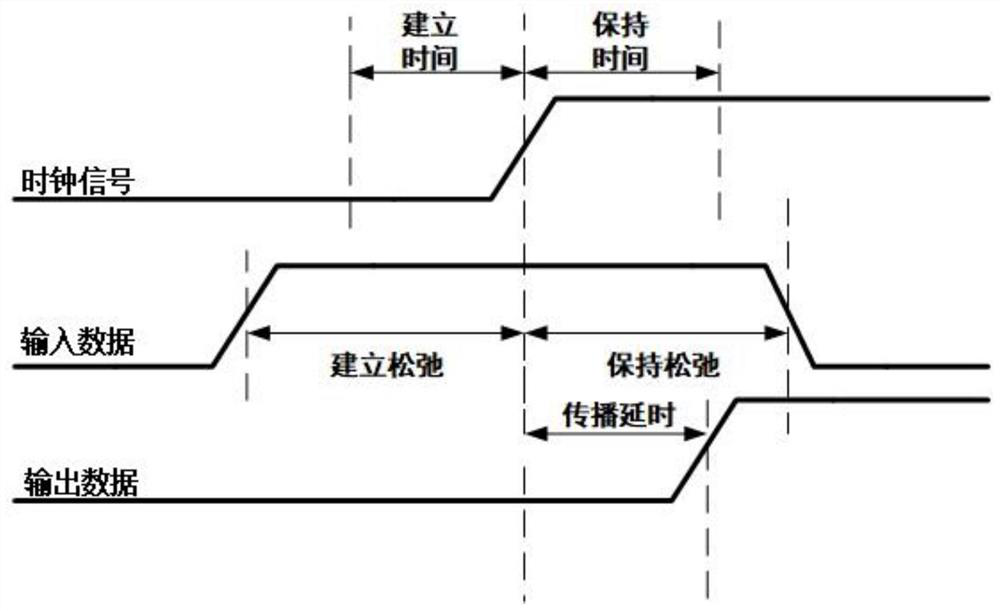

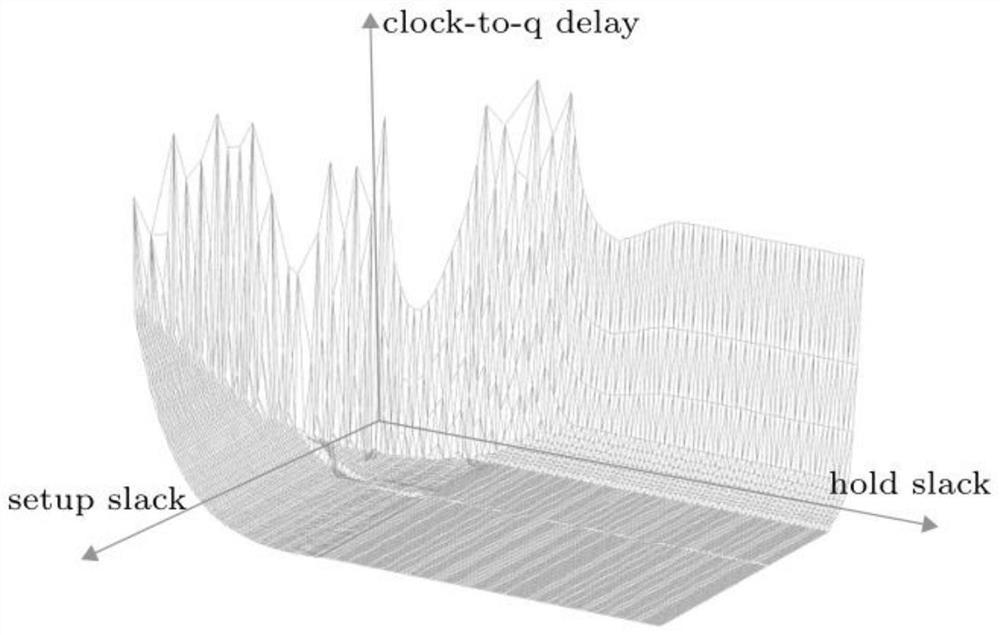

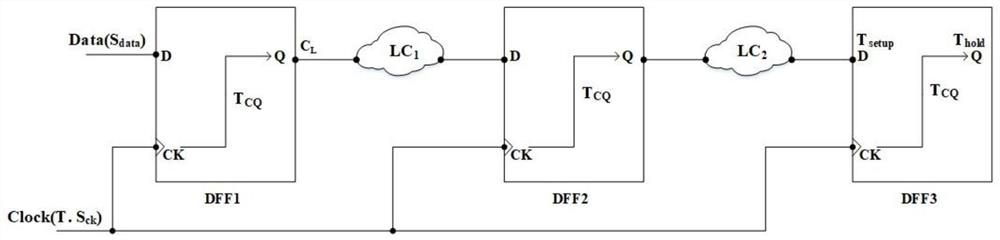

[0025] A circuit timing optimization method based on register flexible timing library, wherein, the register setup time T setup , holding time T hold and the propagation delay T cq Respectively refer to the specific input signal transition time S in the traditional timing library of the register data , clock signal conversion time S ck and register load capacitance C L Combining the minimum time for input data to remain stable before the clock signal jumps, the minimum time for input data to remain stable after the clock signal jumps, and the time interval from clock signal jumps to output data.

[0026] Register establishment slack stay loose and the actual propagation delay respectively refer to the transition time of the input signal at a particular S data , clock signal conversion time S ck and register load capacitance C L The time the input data is a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More