Formation method of semiconductor structure

A semiconductor and functional structure technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems affecting the electrical properties of transistors, achieve the effects of reducing recombination and dissociation, reducing trap defects, and reducing low-frequency noise

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

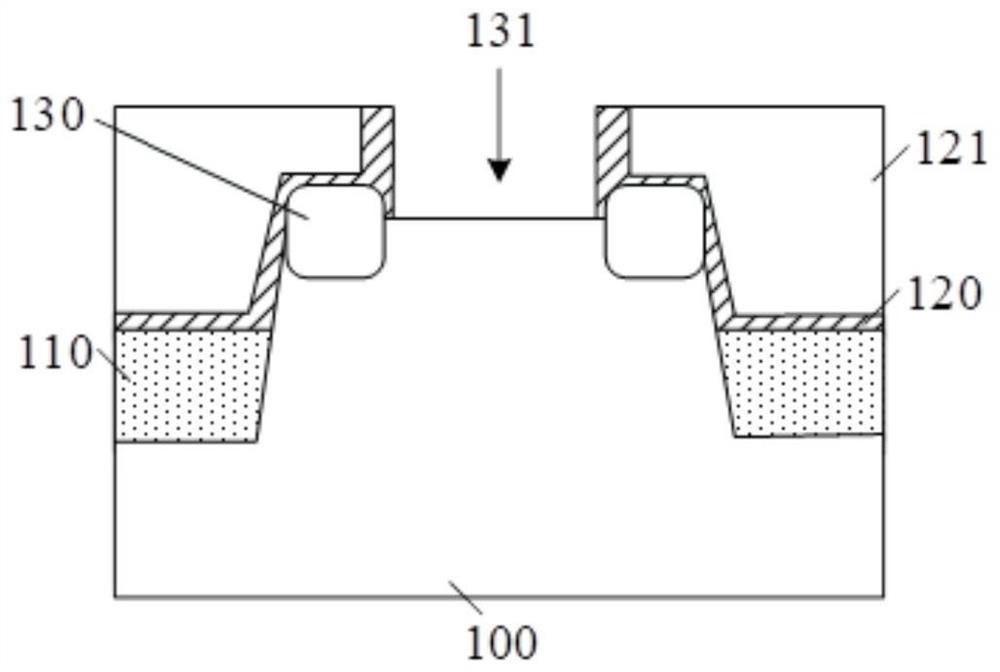

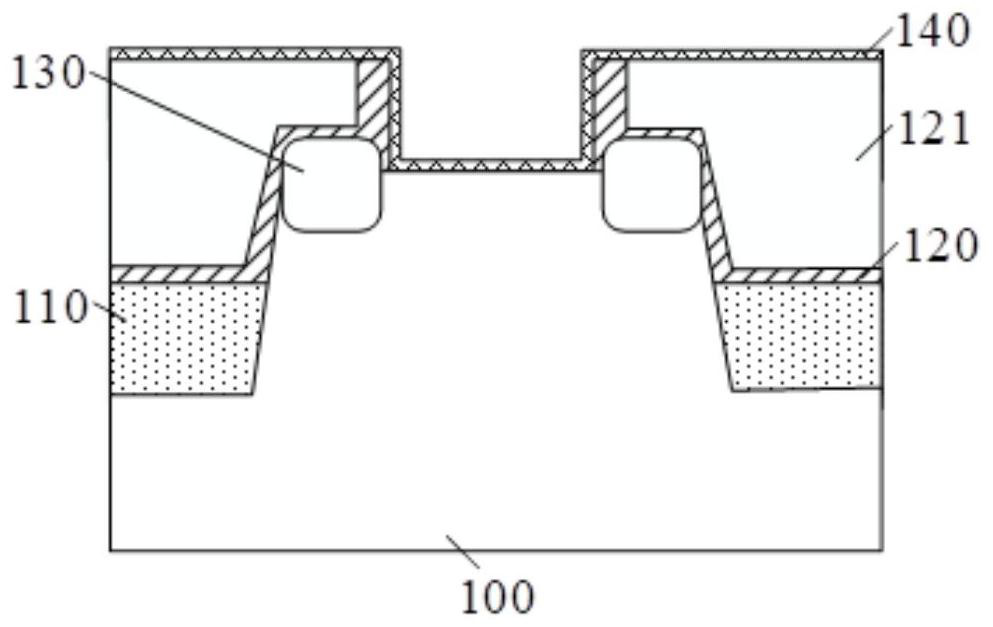

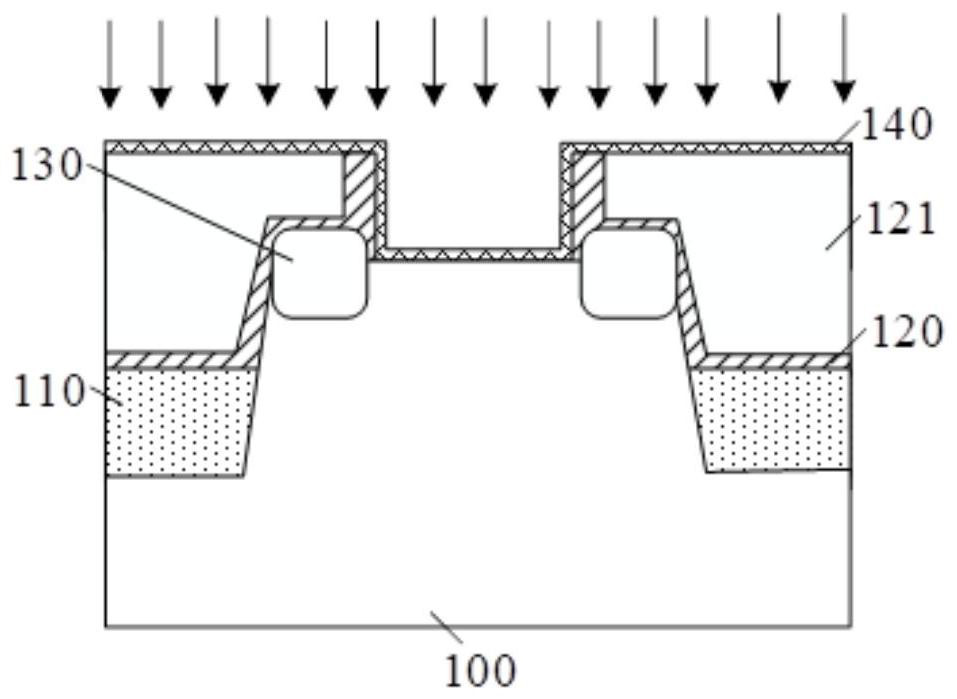

[0028] There are many problems in the semiconductor forming method, for example, the low-frequency noise of the formed semiconductor structure is serious.

[0029] It has been found through research that there are trap defects such as holes or dangling bonds on the surface of the gate dielectric layer of transistors (especially the high-k dielectric layer of oxygen-containing high-k-metal gate transistors), resulting in charged ions (mainly oxygen ions), which are easy to communicate with The trap defects on the surface of the gate dielectric layer recombine and decompose, and the charged ions recombine and decompose repeatedly with the trap defects on the surface of the gate dielectric layer to generate low-frequency electrical signals. This low-frequency noise signal will seriously affect the performance of the transistor.

[0030] A method for reducing low-frequency noise includes: after forming a gate dielectric layer, performing surface passivation treatment on the gate di...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com