Mask, manufacturing method of array substrate, and display panel

A technology of array substrate and mask, which is applied in the field of display panel preparation, can solve the problems of critical size loss and large difference in parasitic capacitance Cgs, etc., and achieve the effects of reducing size loss, improving picture quality, and ensuring processing size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

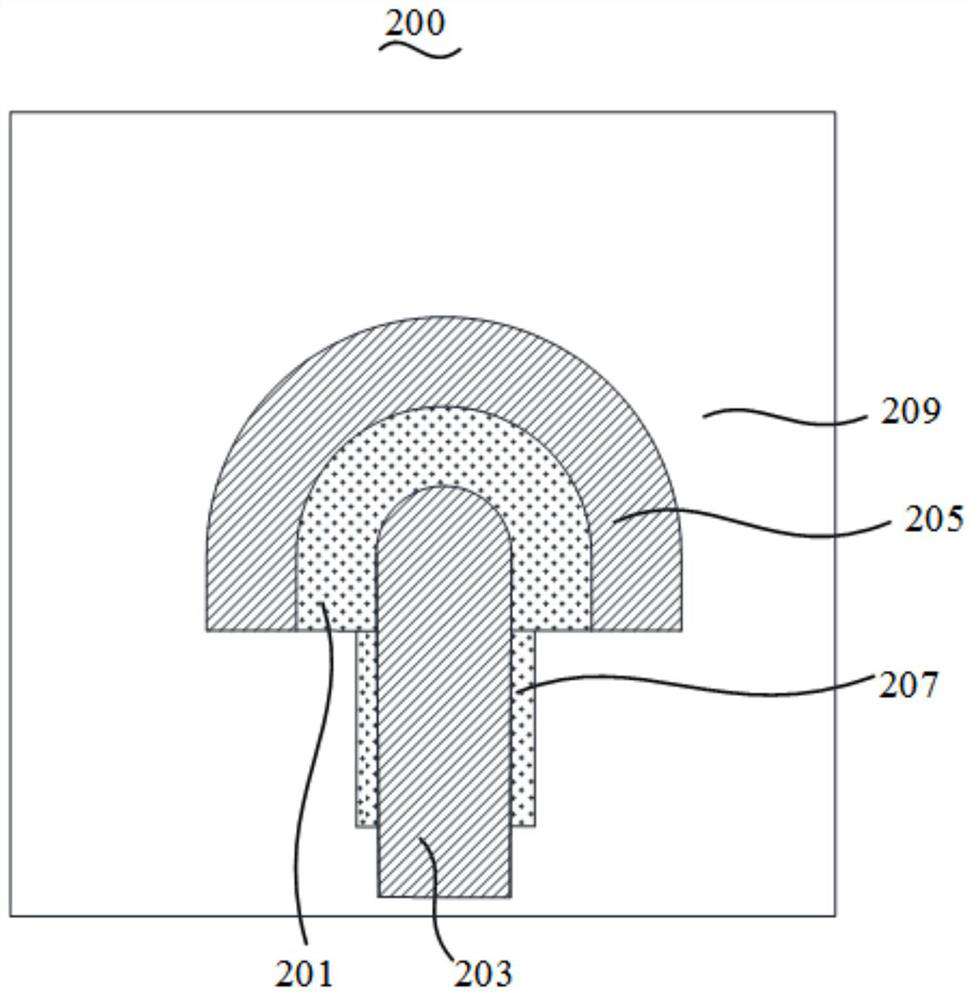

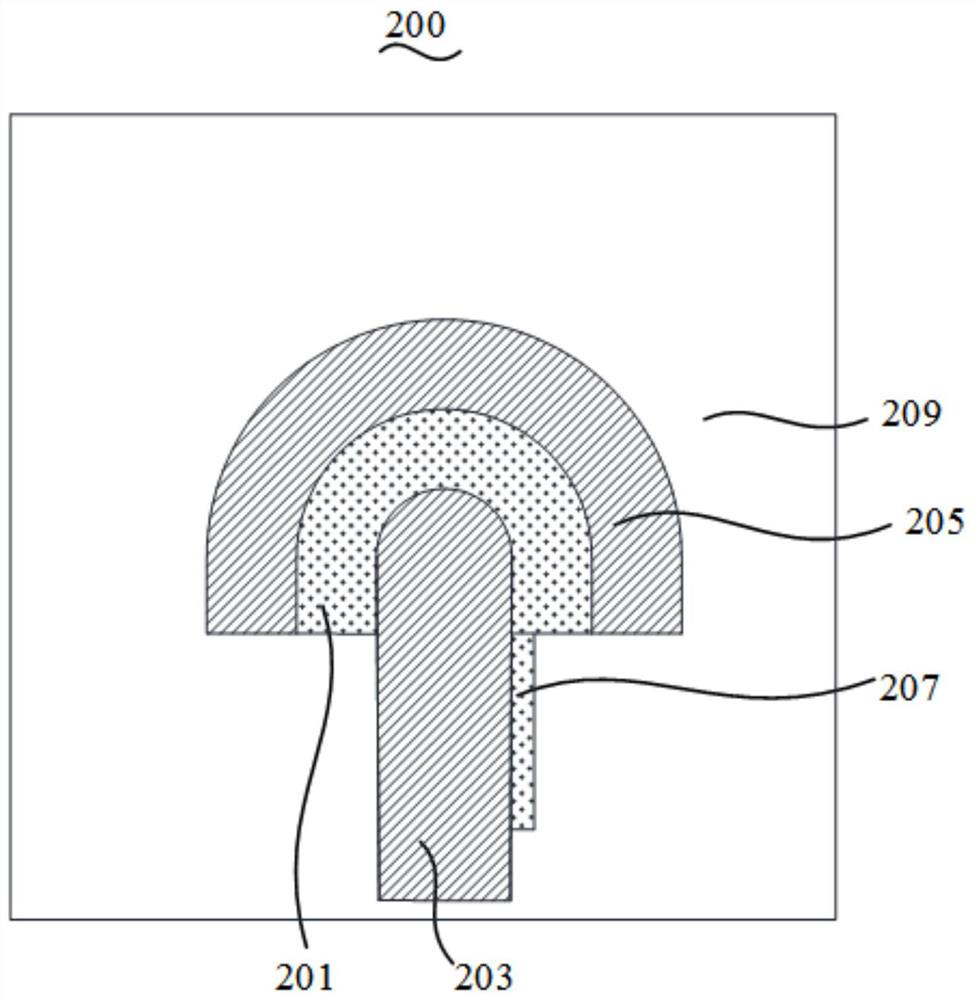

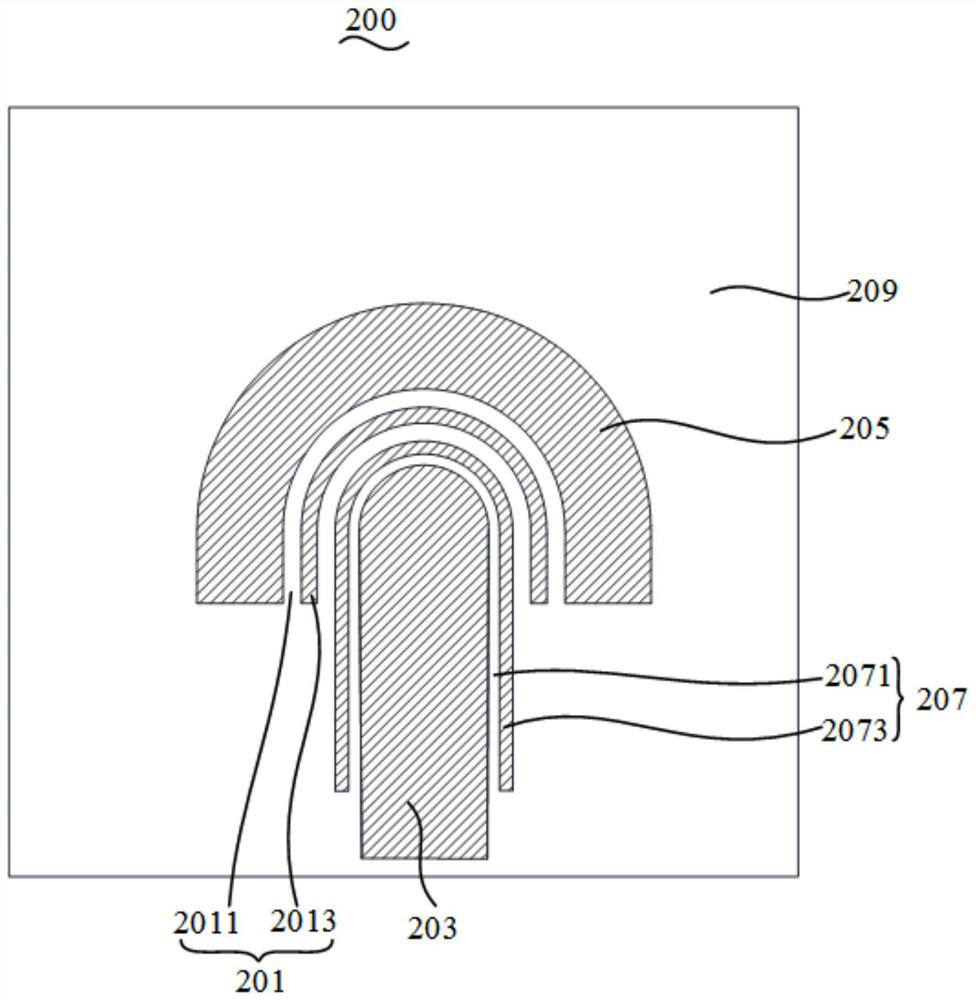

[0040] The present invention provides a mask plate 200 for making an array substrate.

[0041] Please refer to Figure 1 to Figure 4 , it can be seen that the array substrate includes a thin film transistor, and the thin film transistor includes a gate, a source 51 and a drain 53 arranged at intervals, and a channel region 41 is formed between the source 51 and the drain 53 . The mask plate 200 includes: a first exposure region 201 corresponding to the channel region 41 , a second exposure region 203 on one side of the first exposure region 201 where the source electrode 51 is to be formed, and a second exposure region 203 on the side of the first exposure region 201 . The third exposure area 205 where the drain electrode 53 is to be formed on the opposite side of the exposure area 201, and the fourth exposure area 207 located at the edge of the second exposure area 203 that does not overlap with the first exposure area 201 , both the first exposure area 201 and the fourth ex...

Embodiment 2

[0070] Please refer to Figure 5 to Figure 9 , the present invention also provides a method for manufacturing an array substrate using the mask plate of any one of the above embodiments, the method includes the following steps:

[0071] Please combine Figure 6 , step S1: provide a substrate 10, and sequentially form a gate 20, a gate insulating layer 30, a semiconductor layer 40, a metal layer 50 and a photoresist layer on the substrate 10 from bottom to top, and the semiconductor layer 40 corresponds to the A channel region 41 is provided at the position of the gate 20 .

[0072] It can be understood that the array substrate 100 is a multi-layer structure, and each layer structure is formed layer by layer through coating, exposure, development and etching processes, which can be completed through four photolithography (4MASK) processes. Specifically, the array substrate 100 includes a base 10 , which provides a basic carrier. The base 10 is transparent, and its material ma...

Embodiment 3

[0087] Please refer to Figure 10 The present invention also proposes a display panel 300, the display panel 300 includes a color filter substrate 400, an array substrate 100, and a liquid crystal layer 500, the color filter substrate 400 and the array substrate 300 are arranged in pairs, and the array substrate 100 It is prepared by adopting the manufacturing method of the array substrate as described in any of the above embodiments. Since the display panel 300 includes all the technical solutions of all the above-mentioned embodiments, it at least has all the beneficial effects brought by the technical solutions of the above-mentioned embodiments, and will not be repeated here.

[0088] recombine Figure 4 and Figure 9, wherein the array substrate 100 includes a base 10 and a gate 20, an active layer 43, a drain 53, and a source 51 sequentially disposed on the base 10, and the edges of the channel region 41 and the source 51 of the semiconductor layer 40 are masked. The ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| transmittivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More