Preparation method of packaging substrate circuit

A technology for packaging substrates and circuits, applied in multilayer circuit manufacturing, printed circuit manufacturing, printed circuits, etc., can solve problems affecting electrical quality, poor bonding, small area, etc., and achieve good uniformity, good bonding, and increased The effect of subsequent area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

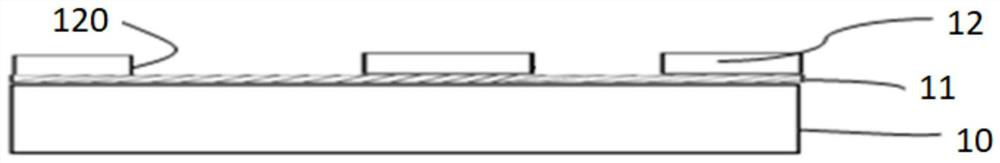

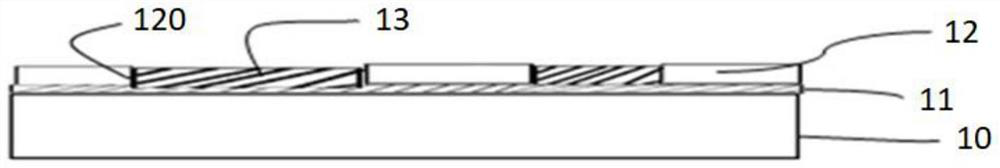

[0050] combine Figure 1A to Figure 1H , the preparation method of the packaging substrate circuit, comprising the following steps:

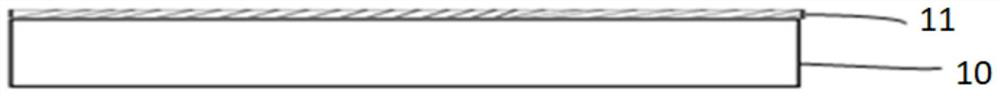

[0051] First, the worker provides a circuit board. The surface of the circuit board is provided with a conductive copper layer.

[0052]Secondly, a first dielectric layer is formed on the surface of the conductive copper layer. The material of the first dielectric layer can be photosensitive or non-photosensitive material, specifically, it can be ABF (Ajinomotobuild-up film), epoxy resin (Epoxy resin), polyimide (Polyimide), cyanate ester (Cyanate Ester), Glass fiber, bismaleimide triazine (Bismaleimide Triazine, BT) or FR5 material mixed with epoxy resin and glass fiber. And a first opening is opened in the first dielectric layer to expose part of the surface of the conductive copper layer. The first opening is formed by laser drilling or exposure and development.

[0053] Secondly, a conductive circuit is formed in the first opening by che...

Embodiment 2

[0059] combine Figure 1A to Figure 1D , Figure 2A to Figure 2D , the preparation method of the packaging substrate circuit, comprising the following steps:

[0060] First, the worker provides a circuit board. The surface of the circuit board is provided with a conductive copper layer.

[0061] Secondly, a first dielectric layer is formed on the surface of the conductive copper layer. The material of the first dielectric layer can be photosensitive or non-photosensitive material, specifically, it can be ABF (Ajinomotobuild-up film), epoxy resin (Epoxy resin), polyimide (Polyimide), cyanate ester (Cyanate Ester), Glass fiber, bismaleimide triazine (Bismaleimide Triazine, BT) or FR5 material mixed with epoxy resin and glass fiber. And a first opening is opened in the first dielectric layer to expose part of the surface of the conductive copper layer. The first opening is formed by laser drilling or exposure and development.

[0062] Secondly, a conductive circuit is forme...

Embodiment 3

[0068] combine Figure 1A to Figure 1D , Figure 3A to Figure 3D , the preparation method of the packaging substrate circuit, comprising the following steps:

[0069] First, the worker provides a circuit board. The surface of the circuit board is provided with a conductive copper layer.

[0070] Secondly, a first dielectric layer is formed on the surface of the conductive copper layer. The material of the first dielectric layer can be photosensitive or non-photosensitive material, specifically, it can be ABF (Ajinomotobuild-up film), epoxy resin (Epoxy resin), polyimide (Polyimide), cyanate ester (Cyanate Ester), Glass fiber, bismaleimide triazine (Bismaleimide Triazine, BT) or FR5 material mixed with epoxy resin and glass fiber. And a first opening is opened in the first dielectric layer to expose part of the surface of the conductive copper layer. The first opening is formed by laser drilling or exposure and development.

[0071] Secondly, a conductive circuit is forme...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More