High-speed burst mode clock data recovery circuit suitable for PAM4 signal

A clock data recovery, burst mode technology, applied in electrical components, electromagnetic receivers, automatic power control and other directions, can solve the problems of increased circuit complexity and power consumption, and achieve the effect of low bandwidth and fast phase locking

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

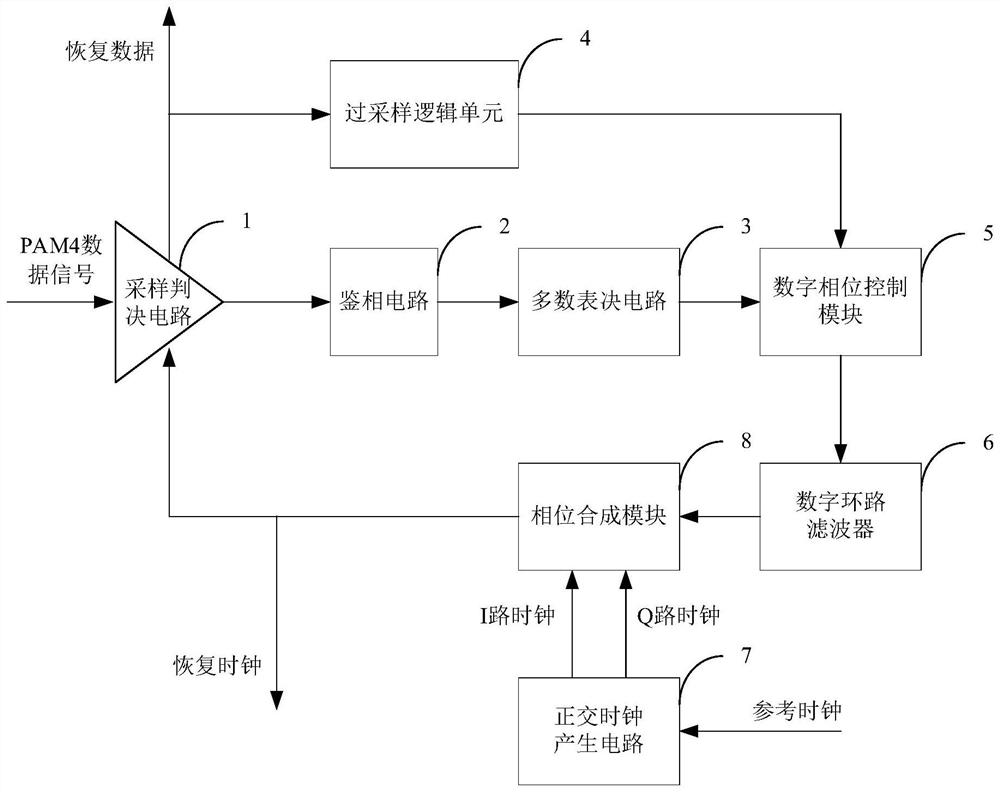

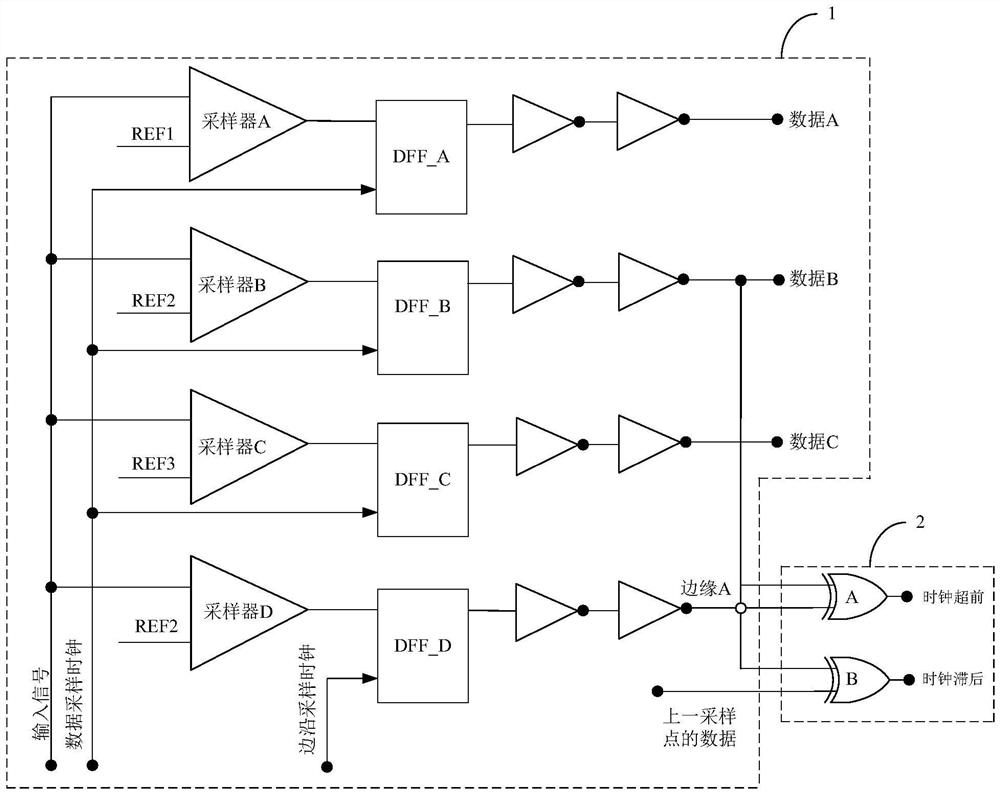

[0032] The present invention is based on the CDR formed by the Bang Bang phase detector and digital loop filter adopted in the prior art, introduces an oversampling logic unit, and realizes an equivalent 3 times oversampling by changing the phase of edge sampling and multiplexing the data sampling unit. Sampling does not introduce a new sampling channel. The introduction of BBPD lock mode and oversampling lock mode enables PAM4CDR in burst mode to lock quickly and improve the jitter characteristics of the recovered clock.

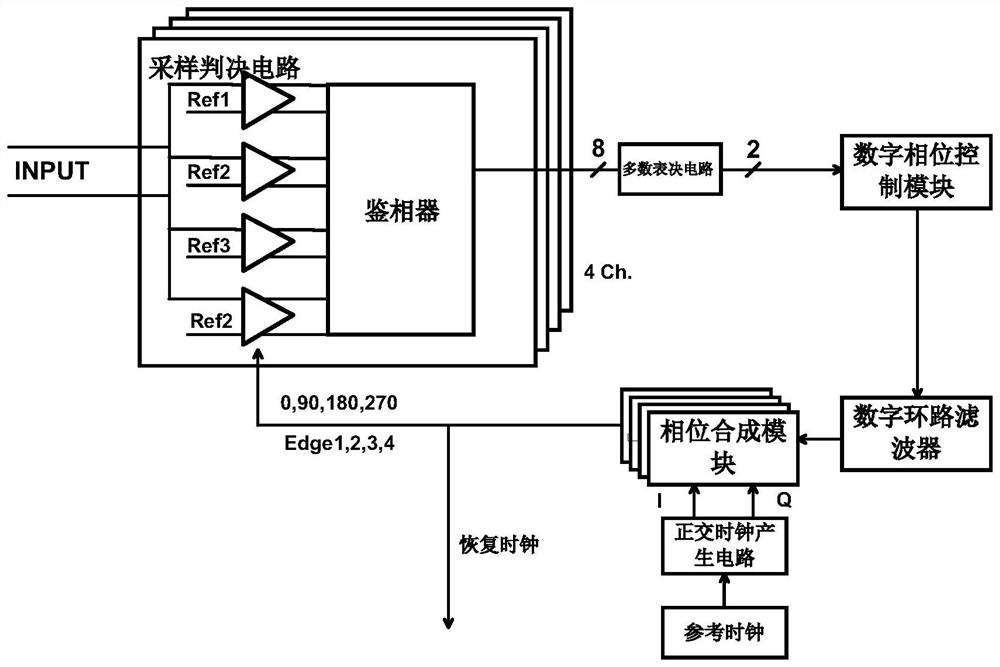

[0033] Such as figure 2 As shown, a kind of high-speed burst mode clock d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More