Intelligent timing synchronization control panel and control method for metro vehicle

A synchronous control, intelligent timing technology, applied in locomotives, AC networks with the same frequency from different sources, AC network circuits, etc., can solve the problems of insufficient timing accuracy, inability to meet, large size, etc. The effect of avoiding electrical failure and high control precision

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

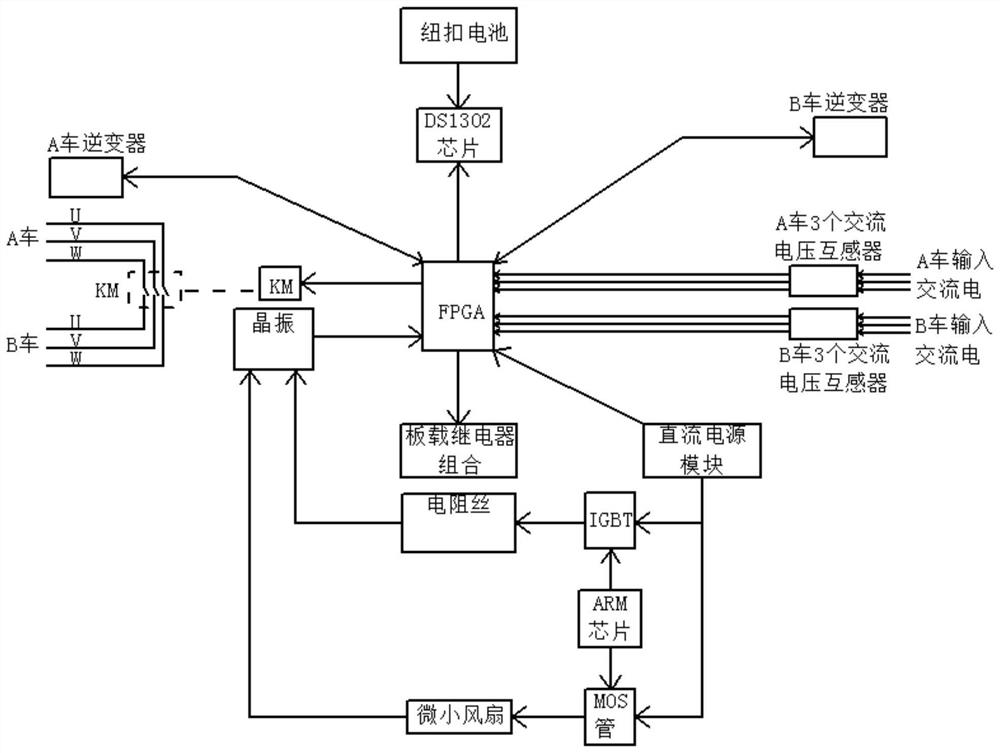

[0041] Such as figure 1 As shown, the subway vehicle intelligent timing synchronization control board of the present invention includes a main control module, an auxiliary control module, a clock module, a DC power supply module and a backup module, wherein:

[0042] The main control module includes the main control chip and the AC contactor KM. The main control chip adopts the FPGA chip. The FPGA chip has the advantages of convenient and flexible programming, high integration, fast processing speed, low power consumption, and high cost performance; the FPGA chip reads the clock The data of the module collects the voltage information of several vehicles, and communicates with the inverters of several vehicles respectively. The AC contactor KM is used to correct and control the AC power of the unreachable vehicles and connect them in parallel after phase synchronization. The FPGA chip is set on the intelligent timing synchronization control board of the subway vehicle, collects...

Embodiment 2

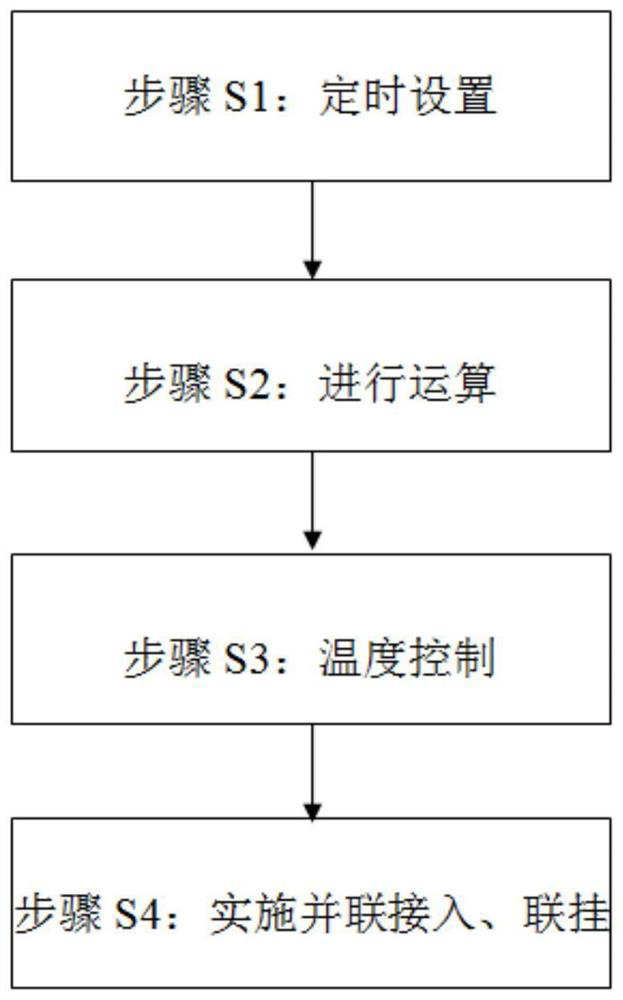

[0050] Such as figure 2 As shown, the control method of the subway vehicle intelligent timing synchronization control panel of the present invention comprises the following steps:

[0051] Step S1: Timing setting: Write the conversion time of the voltage transformers of several vehicles in different phases into the main control chip, that is, the constant array in the FPGA chip program, and obtain the corresponding value by querying the array during use.

[0052] Step S2: Perform calculation: the main control chip (FPGA chip) respectively calculates the time interval after the three-phase AC phase of several vehicles and the delay time interval required by one of the vehicles;

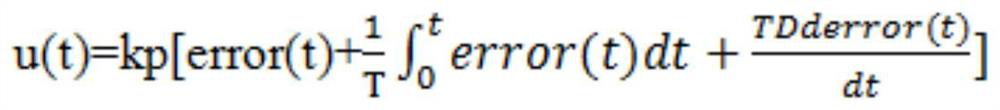

[0053] The formula for calculating the time interval after the three-phase AC phase of several vehicles is as follows:

[0054] Δt 0 =K AS ×(t AUS +t AVS +t AWS ) / 3+K AAD ×(t AUAD +t AAD +t AWAD )3+K ACT ×t ACT -[K BS ×(t BUS +t BVS +t BWS ) / 3+K BAD ×(t BUAD +t BVD +t BWAD )3+K BC...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More