Circuit for configuring, reading back and refreshing SRAM (Static Random Access Memory) type FPGA (Field Programmable Gate Array) and operation method

A circuit and configuration data technology, applied in the direction of instruments, computer control, simulators, etc., can solve the problems of fixed single function, circuit function error, and configuration information lost when power is turned off, so as to overcome the fixed single function and enhance adaptability. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

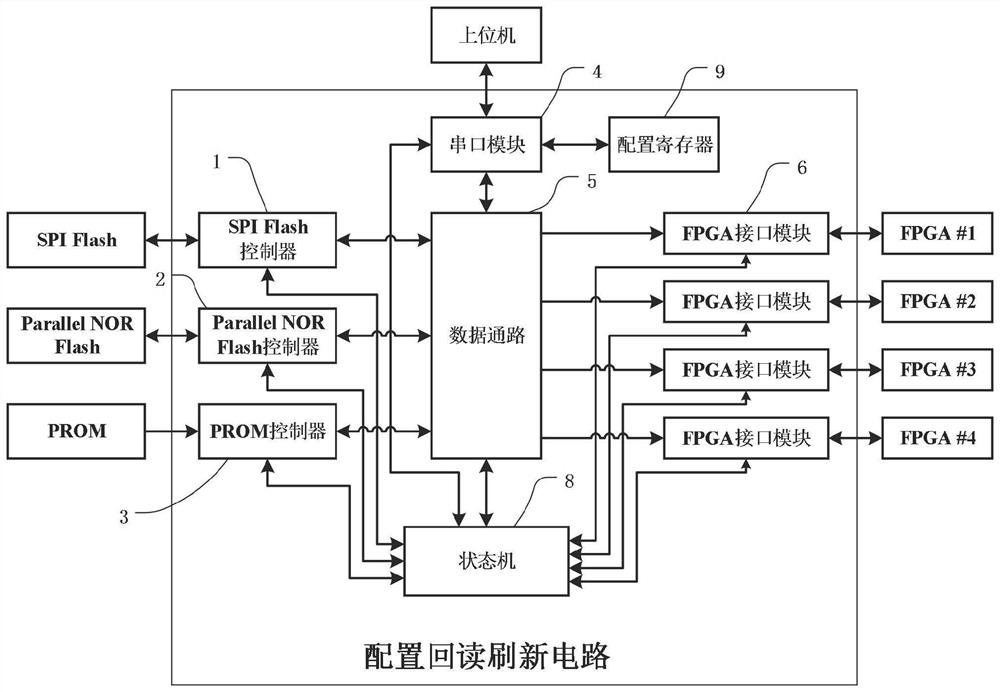

[0072] Depend on figure 1 As shown, a circuit for configuring, reading back and refreshing SRAM FPGA, the circuit includes the following components: SPI Flash controller 1, parallel port NOR Flash controller 2, PROM controller 3, serial port module 4, data path 5, FPGA interface module 6, state machine 8, configuration register 9.

[0073] The SPI Flash controller 1, the parallel port NOR Flash controller 2, and the PROM controller 3 are all memory controllers.

[0074] The SPI Flash controller 1 and the data path 5 carry out two-way data interaction; the SPI Flash controller 1 receives the data sent by the serial port module 4 through the data path 5 and writes it to the SPI Flash; the SPI Flash controller 1 reads The data in the SPI Flash is sent to the serial port module 4 or the FPGA interface module 6 through the data path 5; the SPIFlash controller 1 accepts the control of the state machine 8, and under the control of the state machine 8, the parallel port SPI Flash is ...

Embodiment 2

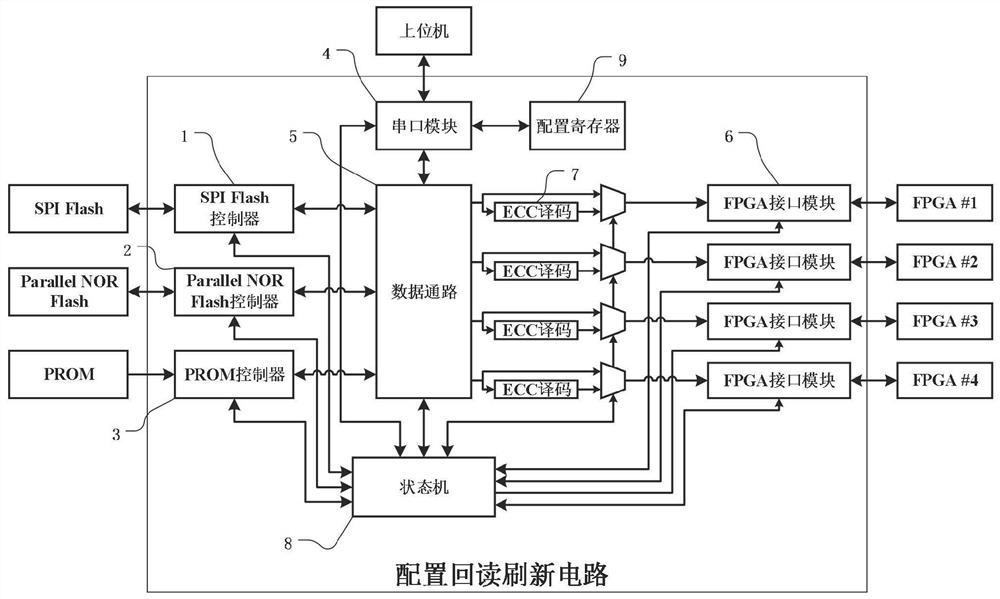

[0091] In order to improve the reliability of the system, on the basis of embodiment 1, by figure 2 As shown, the ECC decoding module 7 is inserted into the circuit: that is, a circuit for configuring, reading back and refreshing the SRAM FPGA, the circuit includes: SPI Flash controller 1, parallel port NOR Flash controller 2, PROM controller 3. Serial port module 4, data path 5, FPGA interface module 6, ECC decoding module 7, state machine 8.

[0092] Described ECC decoding module 7 is connected with FPGA interface module 6;

[0093] When writing data into SPI Flash / NOR Flash / PROM, firstly encode the data with ECC (ErrorCorrection Code), that is, add an error correction and detection code, and then write the encoded data into the corresponding memory. In the present invention, the error correction and error detection code can be added by the user outside the circuit using software in the computer, or can be added by the storage controller inside the circuit. If it is added ...

Embodiment 3

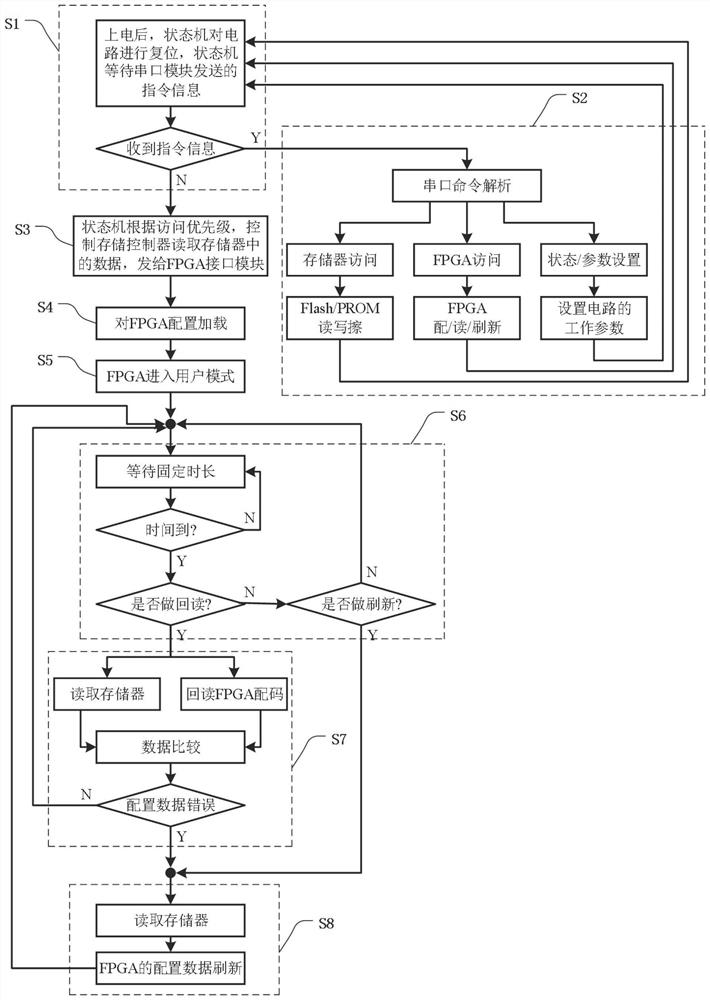

[0098] Based on the circuit structure provided by embodiment 1, by image 3 Shown, a kind of operation method that SRAM type FPGA is configured, read back and refresh of the present invention is as follows:

[0099] S1, after power on, the state machine 8 resets the circuit, then the state machine 8 waits for the instruction information sent by the serial port module 4, and judges whether the instruction information sent by the serial port module 4 is received, that is, the instruction information of the host computer. If the instruction is received, then Execute step S2; if no instruction is received, execute step S3;

[0100] S2, after the state machine 8 receives the command sent by the serial port module 4, that is, the command information of the upper computer, it parses the command, and performs corresponding operations according to the command parsing content:

[0101] If the instruction analysis content is to access the memory, that is, access SPI Flash / NOR Flash / PROM...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More