Fan-out packaging structure and fan-out packaging method

A packaging structure, fan-out technology, applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve the problems of increasing the parasitic effect of the circuit layer and the capacitance effect, the number of conductive holes, and the complex wiring layer process. , to reduce parasitic effects and capacitance effects, simplify process steps, and improve heat dissipation effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0083] To sum up, the fan-out packaging structure 100 and method provided by the embodiments of the present invention have the following beneficial effects:

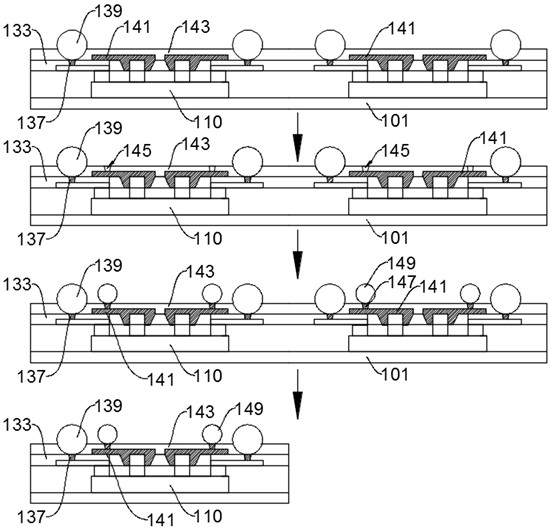

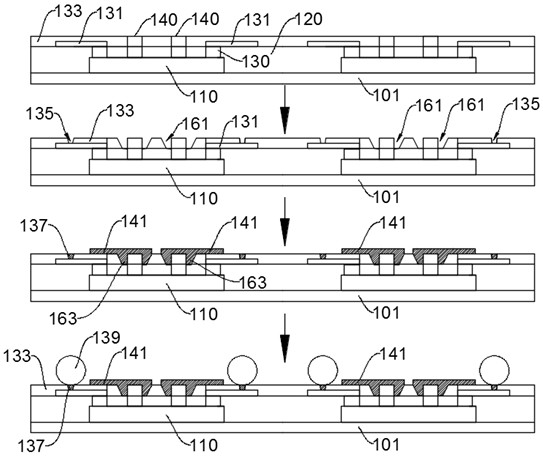

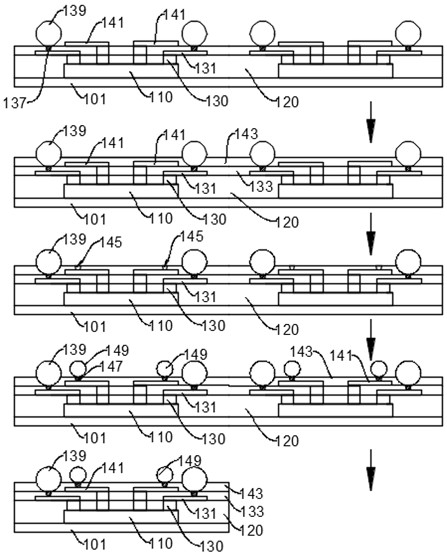

[0084] In the fan-out packaging method provided by the embodiment of the present invention, the first pad 130 and the second pad 140 with different heights are formed on the chip 110, and the first wiring layer is drawn out from the first pad 130 and the second pad 140 respectively. 131 and the second wiring layer 141 can simplify the process without additionally setting conductive holes and conductive columns, while reducing parasitic effects and capacitive effects, avoiding signal transmission interference, and improving product heat dissipation.

[0085] The above is only a specific embodiment of the present invention, but the scope of protection of the present invention is not limited thereto. Anyone skilled in the art can easily think of changes or substitutions within the technical scope disclosed in the present inv...

no. 2 example

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More