EML chip structure with anti-reflection function and preparation method

A chip structure and anti-reflection technology, applied in the structure of optical resonant cavity, final product manufacturing, sustainable manufacturing/processing, etc., can solve optical disturbance, side mode suppression ratio, absorption curve and optical power influence, influence on optical power, etc. problem, to achieve the effect of reducing chirp, excellent anti-reflection, and enhancing anti-reflection characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

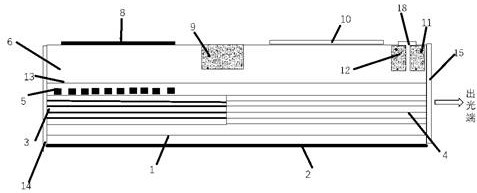

[0062] A preparation method of an EML chip with anti-reflection function, comprising:

[0063] On the InP substrate 1, the DFB quantum well 3 is grown by MOCVD deposition, the material used is InGaAsP, and the growth temperature is 600-800 degrees; using the photolithography technology, the grating layer 5 is etched on the DFB quantum well 3, and on the grating layer 5 The grating cover layer 13 is obtained by using the MOCVD growth technology, and the growth thickness is 100-200 nm.

[0064] Use vapor deposition to generate a SiyOx mask on the grating cover layer 13, x / y is between 1.5~2, use photolithography technology to etch the SiyOx mask layer and one end of the grating cover layer 13, use wet etching and dry The method is etched to stop at the bottom of the DFB quantum well 3 to obtain the first etched region 16 .

[0065] In the first etching region 16, the MOCVD selective region growth technology is used to grow the EAM quantum well 4; the EAM quantum well adopts a d...

Embodiment 1

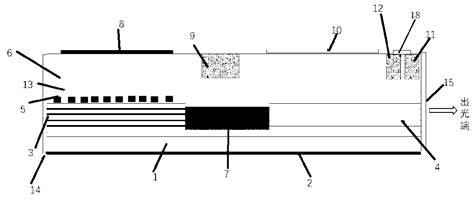

[0072] see Figure 4 , Figure 5 and Image 6 , using MOCVD to grow the DFB quantum well 3 on the InP substrate 1, the material used is InGaAsP, and the growth temperature is 750 degrees; using photolithography technology, the grating layer 5 is etched on the DFB quantum well, and the grating layer 5 is grown by MOCVD technology to obtain a grating cover layer 13 with a growth thickness of 150 nm.

[0073]A SiyOx mask layer is generated on the grating cover layer 13, x / y = 2, the SiyOx mask layer and one end of the grating cover layer 13 are etched using a photolithography technique, and wet etching and dry etching are used to etch to The bottom of the DFB quantum well 3 stops to obtain the first etching region 16; in the first etching region 16, the MOCVD selective region growth technology is used to grow the EAM quantum well 4;

[0074] In the first etching region 16, the MOCVD selective region growth technology is used to grow the EAM quantum well 4; the EAM quantum well...

Embodiment 2

[0079] On the InP substrate 1, MOCVD is used to grow the DFB quantum well 3, the material used is InGaAsP, and the growth temperature is 750 degrees; the photolithography technology is used to etch the grating layer 5 on the DFB quantum well, and the MOCVD growth technology is used on the grating layer 5. The grating cover layer 13 was obtained, and the growth thickness was 150 nm.

[0080] A SiyOx mask layer is generated on the grating cover layer 13, x / y = 2, the SiyOx mask layer and one end of the grating cover layer 13 are etched using a photolithography technique, and wet etching and dry etching are used to etch to The bottom of the DFB quantum well 3 stops to obtain the first etching region 16; in the first etching region 16, the MOCVD selective region growth technology is used to grow the EAM quantum well 4;

[0081] see Figure 4 , Figure 5 and Figure 7 , using the MOCVD selective region growth technology in the first etching region 16 to grow the EAM quantum well...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| wavelength | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More