Self-purification method for reducing Dimple rate in Gringing process

A self-purification, silicon wafer technology, applied in machine tools, manufacturing tools, grinders and other directions suitable for grinding workpiece planes, can solve problems such as increasing the scrap rate of silicon wafers, increasing the overall cost of production and processing, and affecting nanometer topography.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0020] The self-purification method of the present embodiment comprises the following steps:

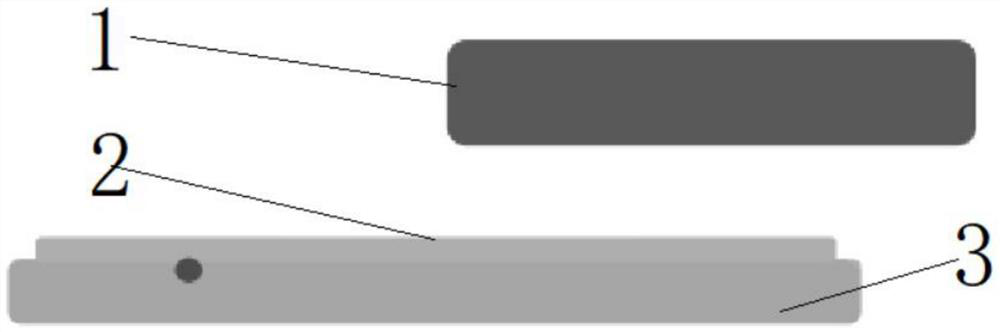

[0021] S1. First, prepare the silicon wafer material to be processed for use, and release the vacuum through the Table to generate suction, adsorb the silicon wafer to be processed on its surface, and use a grinding wheel to grind and purify the silicon wafer from above in real time.

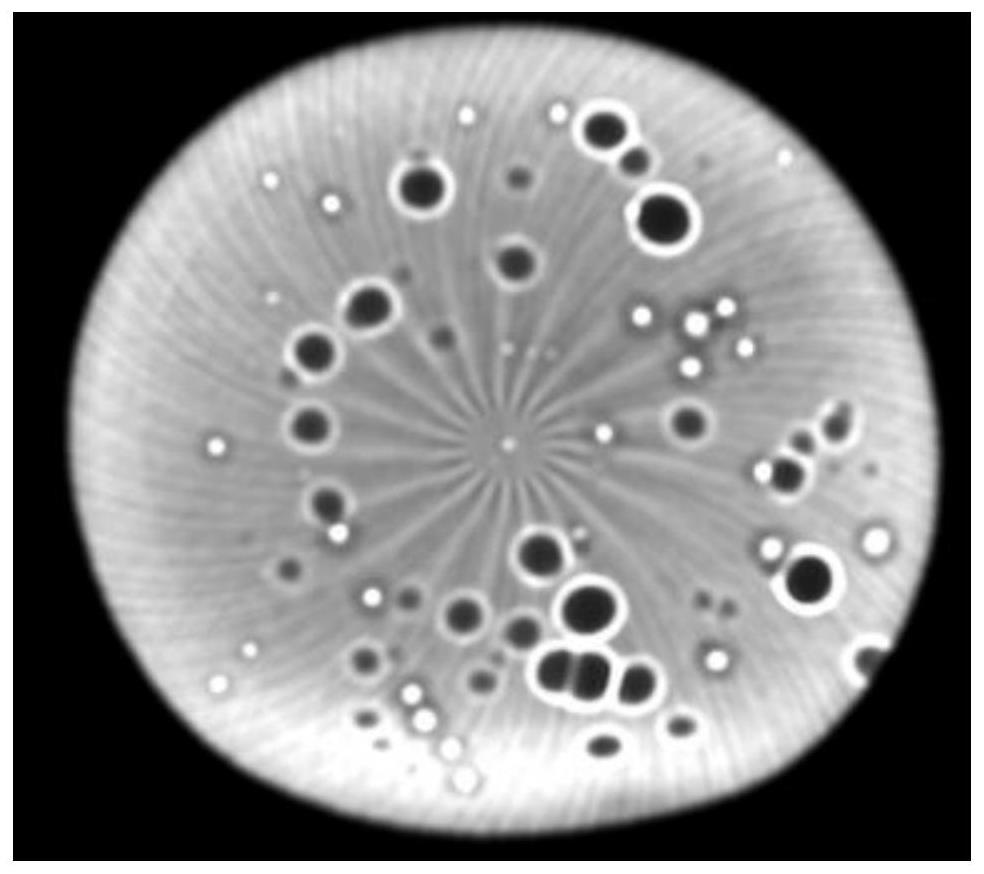

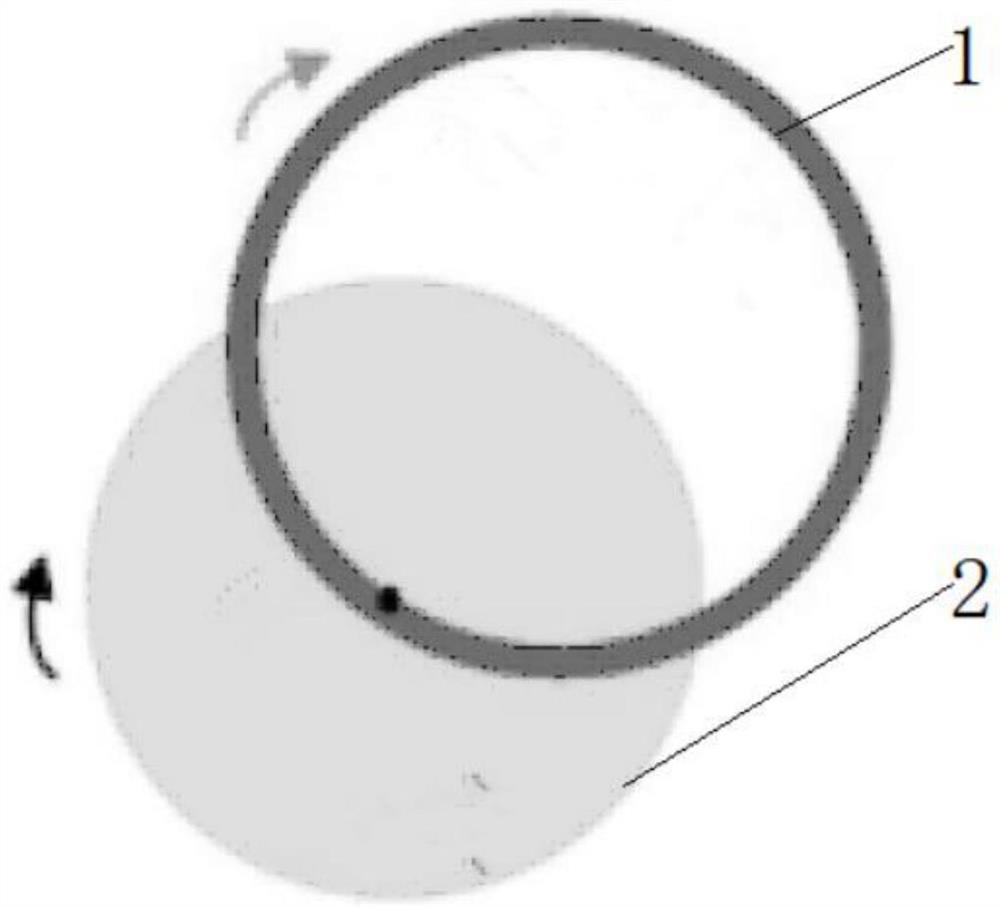

[0022] S2. Then in the process of grinding and purification, according to the actual needs of grinding and purification, personnel can adjust the rotation speed of the table in real time, so that the rotation speed of the table can be adjusted to a minimum, thereby effectively reducing the influence of centrifugal force and avoiding the lack of ceramic holes on the edge. , the edge impurities are not easy to be excluded and the edge Dimple problem has a greater impact on the back pass, which makes the back pass more difficult to repair.

[0023] S3. Finally, increase the air volume in the outer ring of...

Embodiment 2

[0027] The difference with the first embodiment is:

[0028] The self-purification method of the present embodiment comprises the following steps:

[0029] First, prepare the silicon wafer material to be processed for standby, and release the vacuum through the Table to generate suction, adsorb the silicon wafer to be processed on its surface, and use the grinding wheel to grind and purify the silicon wafer from above in real time, and set the grinding wheel to process The process speed is equal to the purification (that is, the non-grinding process) speed, and the speed of the table processing process is set equal to the purification (that is, the non-grinding process) speed, and the air blowing volume and the water blowing flow of each hole of the table ceramic hole are set to be the same. .

[0030] To sum up: the results of the present invention in Example 1 of the present invention show that, compared with the results of the traditional self-cleaning method in Example 2,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More