Silicon carbide wafer back surface processing technology

A processing technology, silicon carbide technology, used in sustainable manufacturing/processing, final product manufacturing, semiconductor/solid-state device manufacturing, etc., which can solve the problems of high wafer fragmentation rate and large grinding volume.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0059] like Figure 1-Figure 7 As shown, a backside manufacturing process of a silicon carbide wafer specifically includes the following steps:

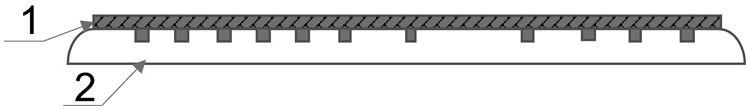

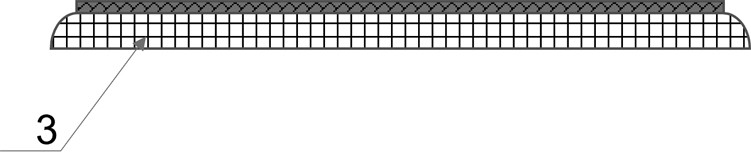

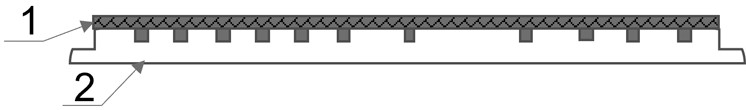

[0060] S1. The first SiC carrier 3 and the SiC wafer 2 that has completed the front-side process are thermally oxidized to SiO 2 Layer 1 growth; thermal oxidation of SiO 2 Layer 1 is grown to a thickness of 100-150 nm; as Figure 1-2 shown;

[0061] S2. Trimming process for SiC wafer 2: In order to ensure the quality of subsequent wafer thinning, the wafer trimming depth should be greater than the same wafer thinning thickness, and the wafer trimming depth range is between 100-200um; The stability of the wafer trimming process. In step S2, the wafer trimming can be performed by multiple trimming methods. The width of each trimming does not exceed 2mm and the depth does not exceed 100um. The specific steps are:

[0062] Step S201, trimming the SiC wafer 2 for the first time, the trimming width is 2mm, and the depth is 100um;

[0...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More