Electronic package for electronic element and manufacturing method thereof

A technology for electronic packaging and conductive parts, applied in the field of organic multi-layer interconnection structures, can solve problems such as increasing the cost of electronic packaging and limiting the electrical performance of organic electronic packaging.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

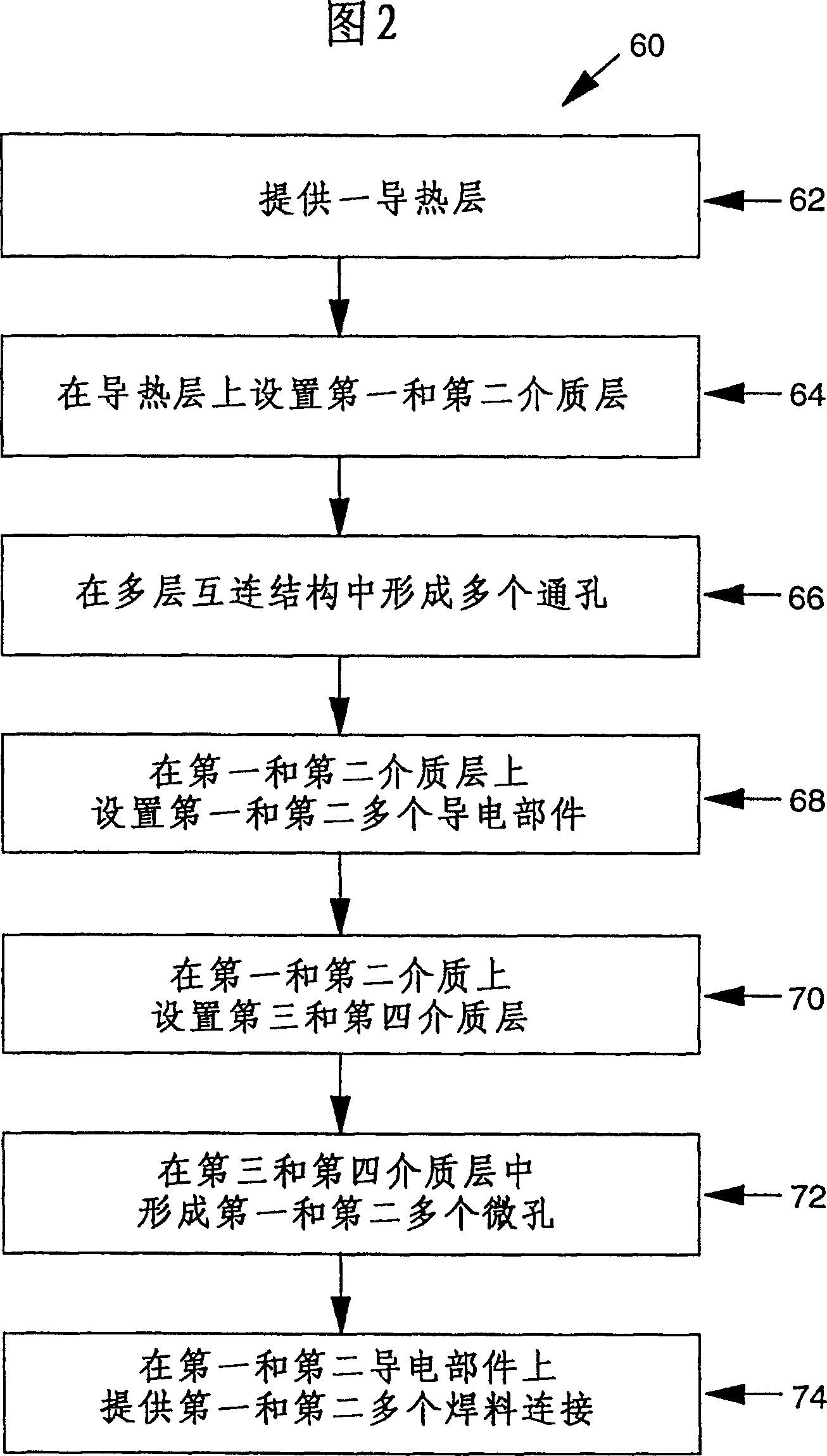

[0022] The present invention provides an electronic package comprising a multilayer interconnection structure (organic chip carrier) and a semiconductor chip, the multilayer interconnection structure is relatively compliant and has a CTE of about 10 to 12 parts per million per degree Celsius, substantially preventing Failure of the interconnect between the semiconductor chip and the printed circuit board on which the package will be assembled.

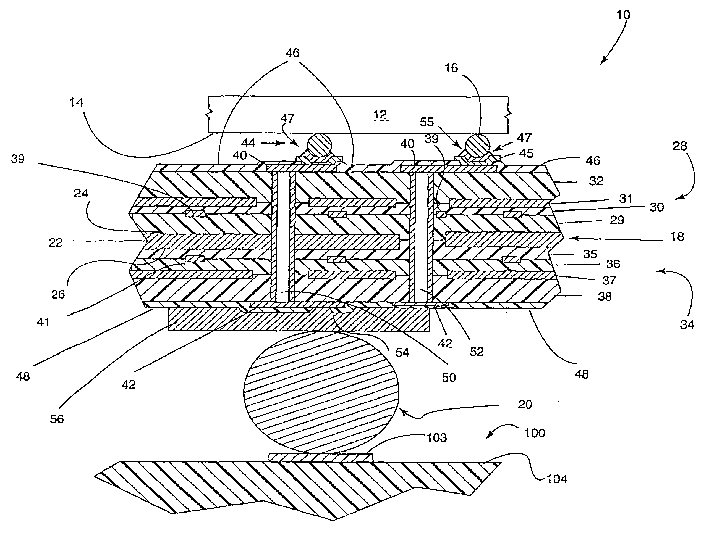

[0023] Referring to FIG. 1 , a front partial cross-sectional view of one embodiment of an electronic package 10 of the present invention is shown. The electronic package 10 includes a semiconductor chip 12 having a first surface 14 including a plurality of contact features 16 thereon. The plurality of contact features are preferably solder balls that control the collapse of the chip connections (C4), each connected to a respective contact (not shown) on the first surface 14 of the chip. Other contact member shapes used in the present ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com