Field effect transistors with improved implants and method for making such transistors

A field-effect transistor, transistor technology, applied in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., to achieve the effect of performance improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

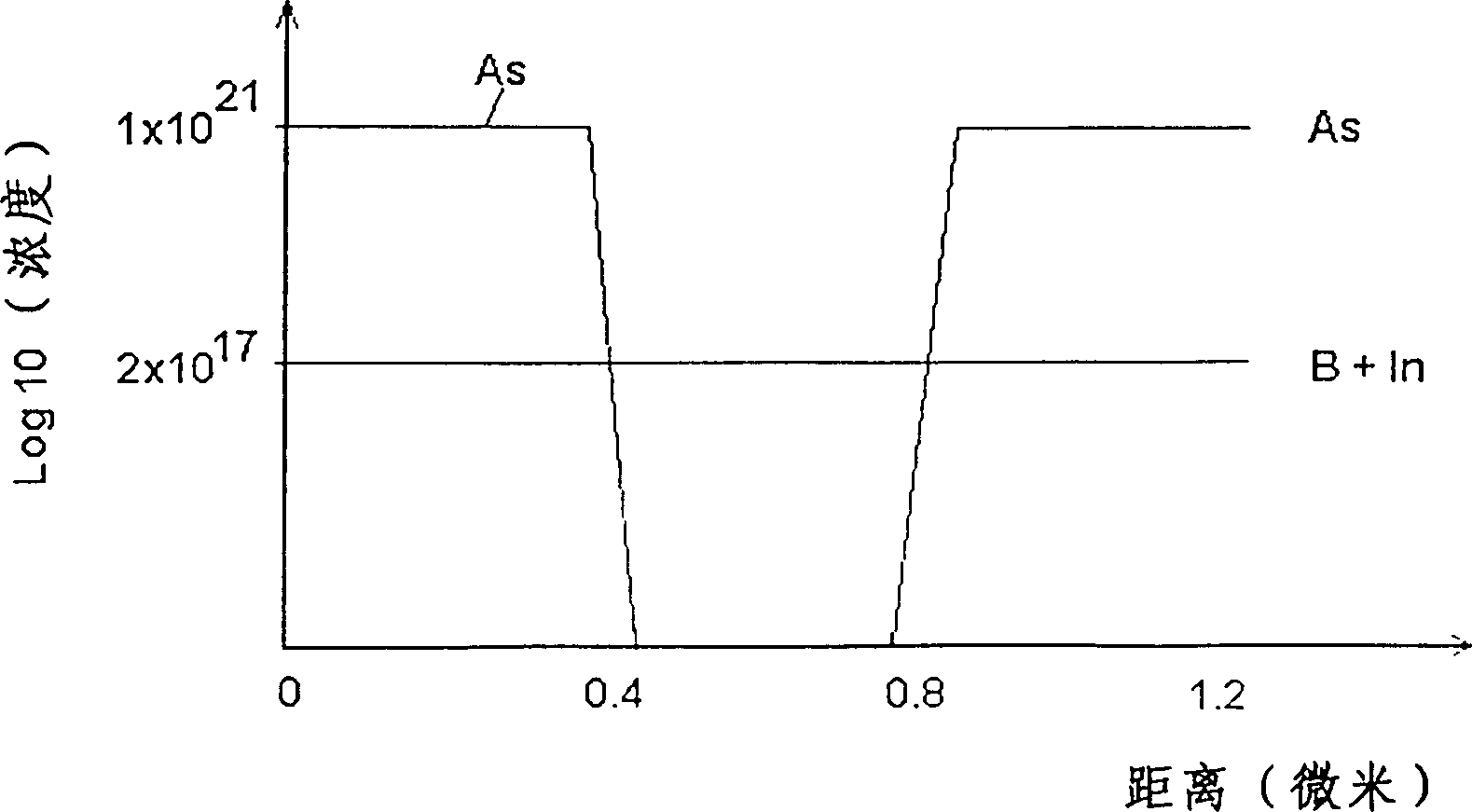

[0053] In this article, n + or p +Doped semiconductor means heavily doped semiconductor. Typically they have at least 10 19 to 10 22 / cm 3 the dopant concentration. The n or p doped region typically has 1×10 17 to 1×10 18 / cm 3 The dopant concentration of n - or p - The doped region has approximately 10 16 / cm 3 the dopant concentration.

[0054] When the word FET is used herein, it means any kind of field effect transistor, including MOSFET, CMOS FET, NMOS, PMOS, and the like.

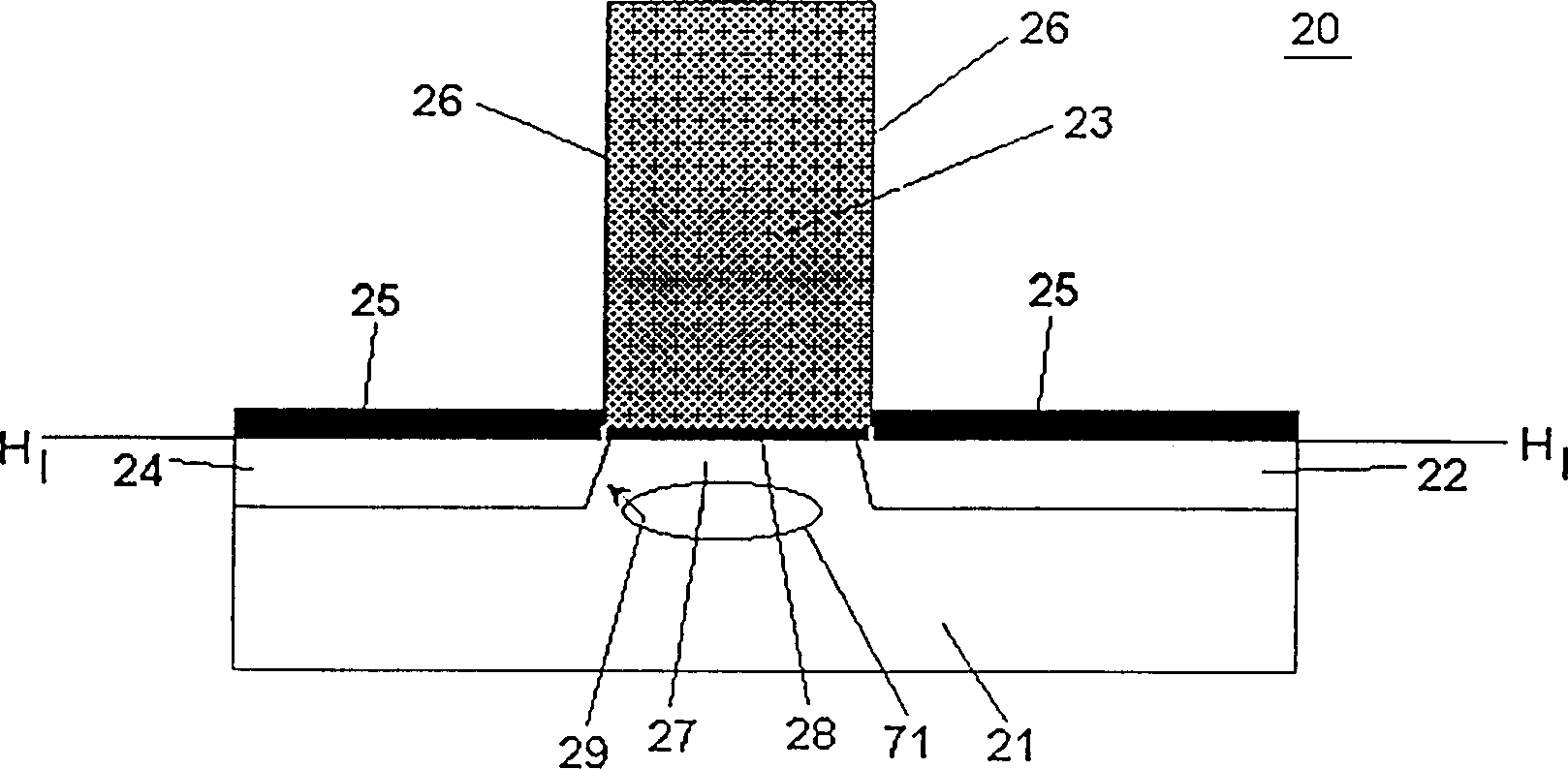

[0055] exist Figure 2A A FET 20 according to the present invention is illustrated in . It is formed in the semiconductor substrate 21 . The substrate may be, for example, a silicon substrate. In this example, by n + Doped to define drain region 22 and source region 24 . Impurities well suited for n-type doping are, for example: P, As and Sb. As is used as a dopant in this embodiment. For defining p-type source and drain regions, B, In and Ga can be used. The polysilicon gate 23 si...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More