Method for preparing capacitor in semiconductor assembly

A technology for semiconductors and capacitors, which is applied in the field of using a ring-shaped Si3N4 to prepare capacitors in semiconductor components, which can solve difficult problems such as dielectric layer thickness, oxidation resistance reduction, and oxidation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

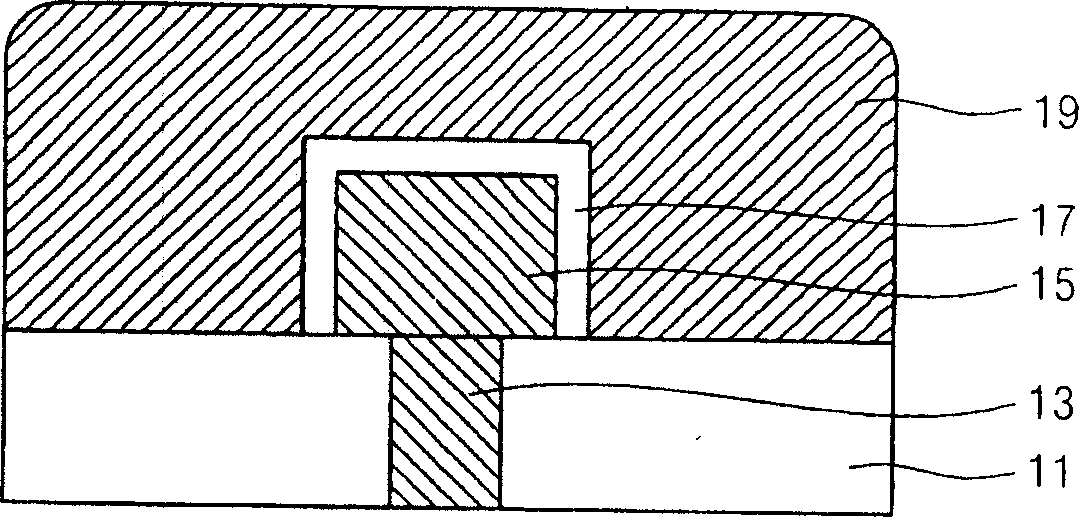

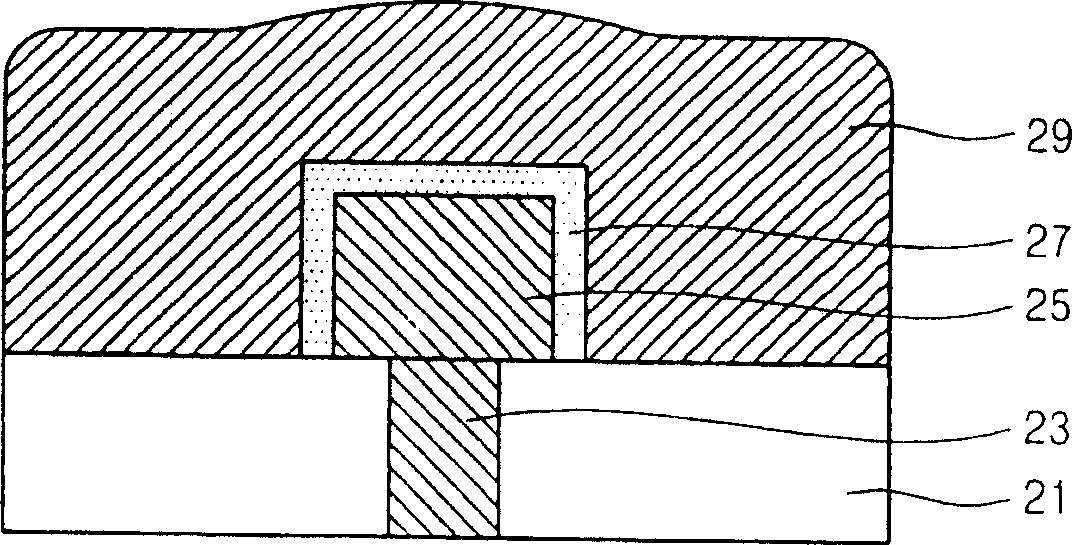

[0014] Hereinafter, a preferred embodiment of the present invention will be described in detail with reference to the drawings. In the following description and the drawings, the same reference numerals are used to denote the same or similar elements, so repeated descriptions of the same or similar elements in the description are omitted.

[0015] Such as figure 2 As shown, it relates to a method for manufacturing a capacitor in a semiconductor component of the present invention. The interlayer insulating layer 21 is deposited on a wafer (not shown), in which some elements are formed, and the selective layout pattern of the interlayer insulating layer is scribed to form contact holes (not shown) that can expose part of the semiconductor wafer .

[0016] Next, a contact plug 23 is formed in a contact hole (not shown), and a cylindrical, recessed, or other storage node 25 is formed on the entire surface of the semiconductor wafer.

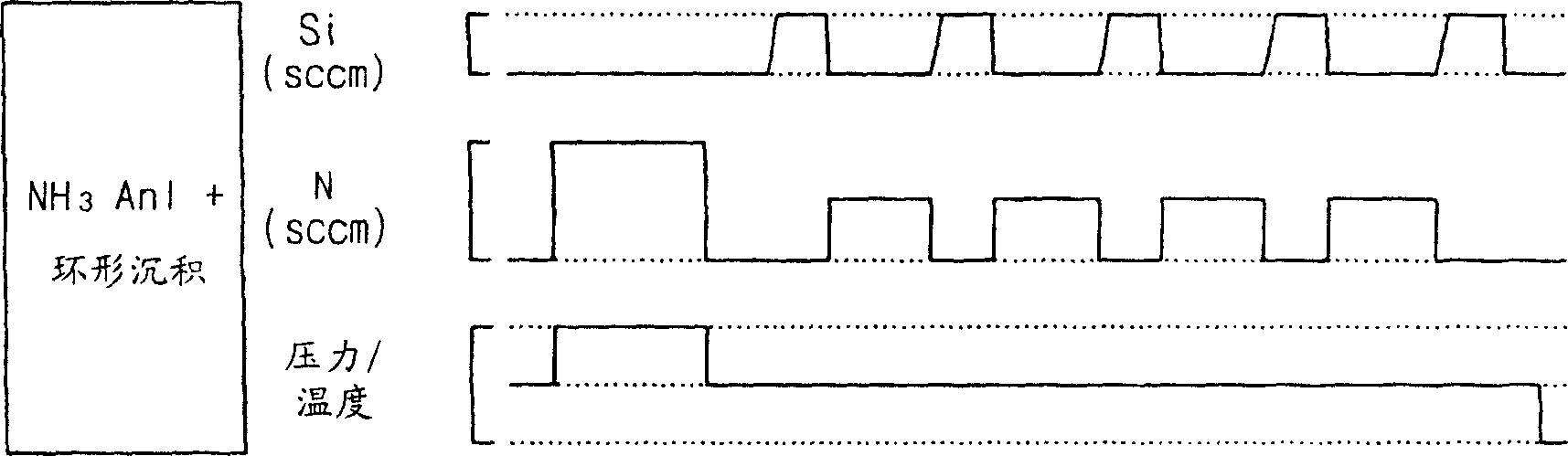

[0017] Then, by the ring Si 3 N 4 Or SiO x N y (W...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More