Ball grid array semiconductor package

A ball grid array, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of destruction, inability to change, insufficient change, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

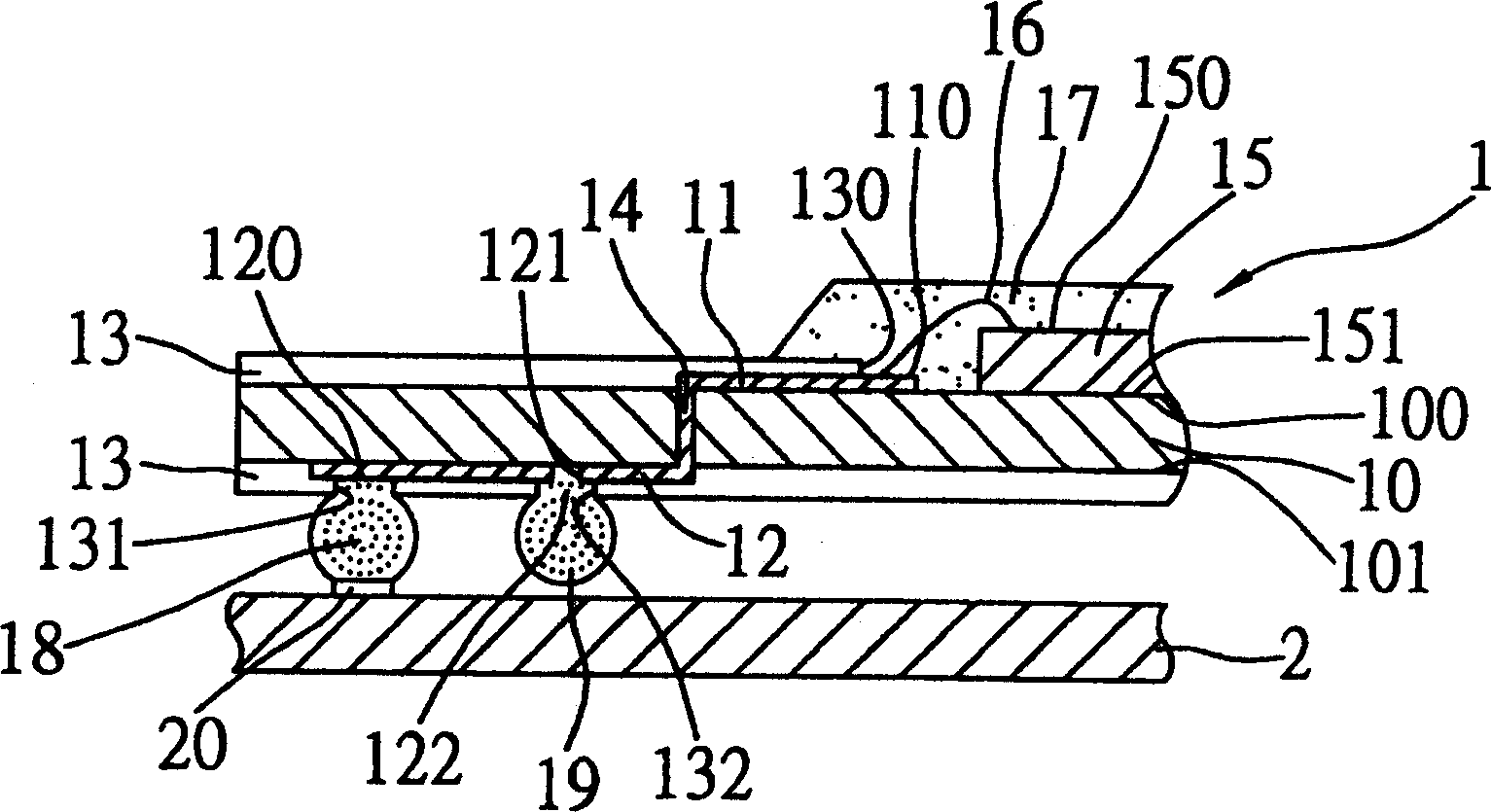

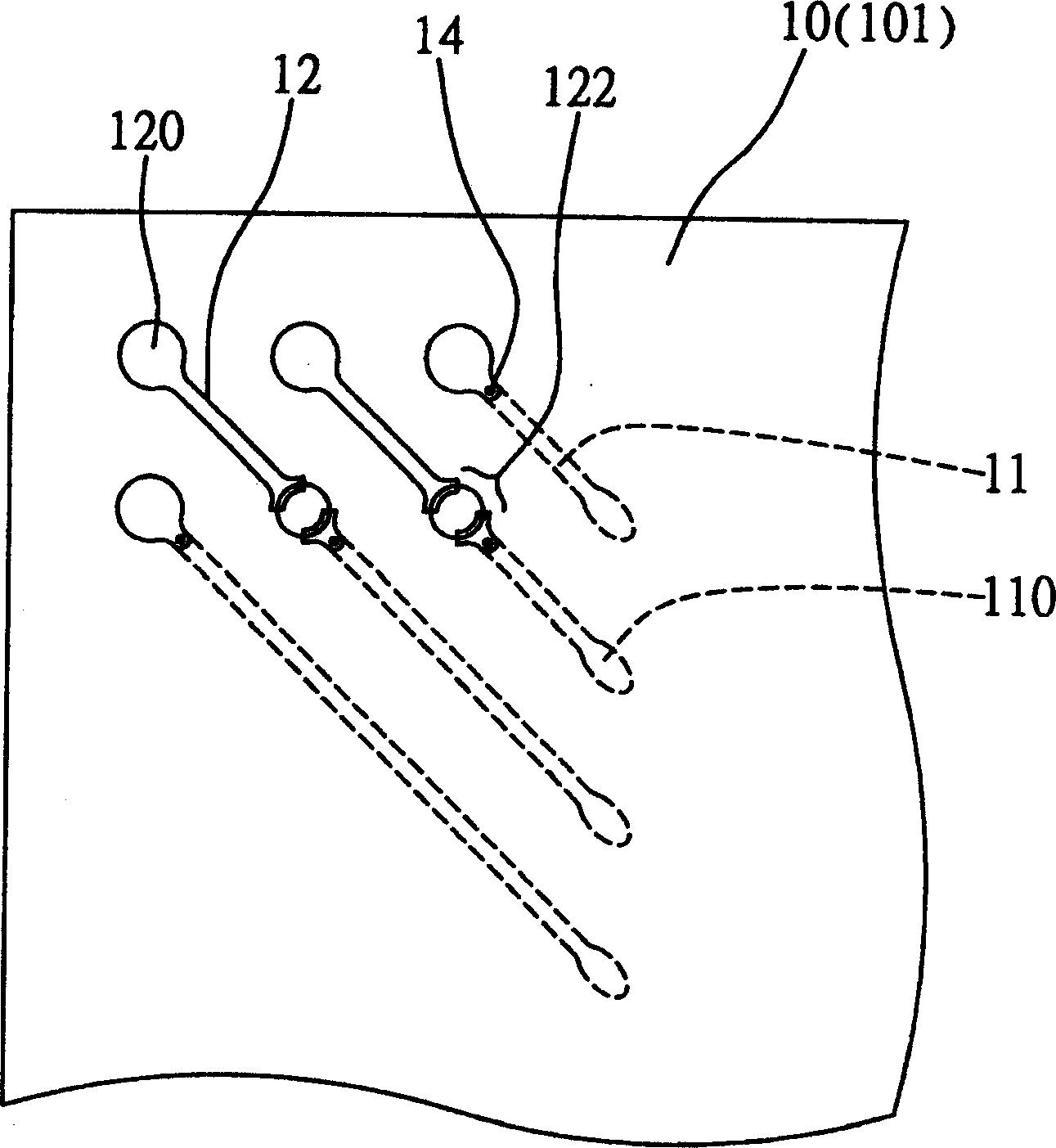

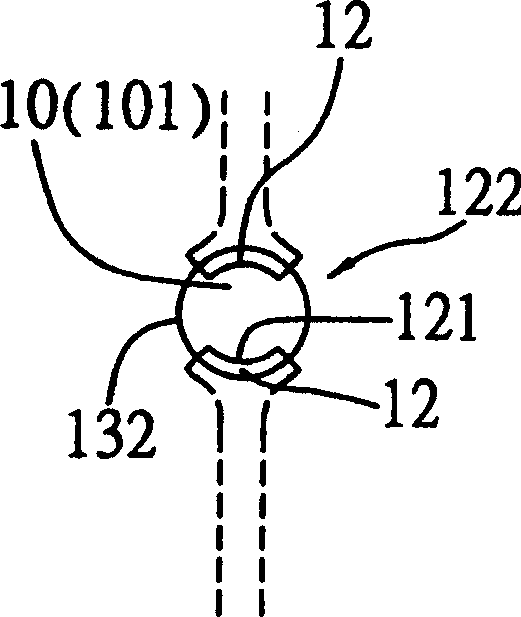

[0026] Such as figure 1As shown, the semiconductor package 1 of Embodiment 1 of the present invention is a ball grid array packaging structure using a substrate 10 as a chip carrier (Chip Carrier), and the substrate 10 can be made of existing resin materials, such as epoxy resin (Epoxy Resin) ), polyimide (Polyimide) resin, BT (Bismaleimide Triazine) resin, FR4 resin, FR5 resin, etc. The substrate 10 has an upper surface 100 and an opposite lower surface 101, a plurality of first conductive traces 11 are laid on the upper surface 100 of the substrate 10, and a plurality of second conductive traces are formed on the lower surface 101 of the substrate 10 The wire 12 , the conductive traces 11 , 12 each have a terminal 110 , 120 . The conductive traces 11, 12 are formed by passing at least one copper foil (Copper Foil, not shown) bonded on the upper and lower surfaces 100, 101 of the substrate 10 through existing exposure (Exposing), developing (Developing) , etching (Etching) ...

Embodiment 2

[0037] Figure 6 A semiconductor package 1' of Embodiment 2 of the present invention is shown. As shown in the figure, the structure of this semiconductor package 1' is roughly the same as that of Embodiment 1 ( figure 1 ) is the same as the semiconductor package 1 , the difference is that the discontinuous pads 122 and the first solder balls 19 are arranged on the upper surface 100 of the substrate 10 . That is, the discontinuous pad 122 is formed on the upper surface 100 of the substrate 10 at the non-terminal (or welding finger) 110 position of the predetermined first conductive trace 11, so that the discontinuous pad 122 and the first implanted thereon The solder ball 19 is not covered by the encapsulant 17, so that the first solder ball 19 can be removed or pushed away from the discontinuous pad 122 as required; also, the discontinuous pad 122 and the first solder ball 19 are arranged on the The upper surface 100 of the substrate 10 does not occupy the area for the inpu...

Embodiment 3

[0039] Figure 7A Shows the semiconductor package 1 " of embodiment 3 of the present invention. As shown in the figure, the structure of this semiconductor package 1 " is roughly the same as that of embodiment 1 ( figure 1 ) is the same as the semiconductor package 1, the difference is that the terminal portion of the predetermined second conductive trace 12 on the lower surface 101 of the substrate 10 is to form a discontinuous pad 122 instead of forming an input / output pad; that is, the The second conductive trace 12 formed with the discontinuous pad 122 is electrically connected to the solder finger 110 connected to the solder wire 16 on the upper surface 100 of the substrate 10 through the corresponding conductive through hole 14, and is not connected to the solder finger 110 as an input / output The second solder ball 18 or the output / input pad 120 at the end forms an electrical connection.

[0040] When the functions of these chips are to be controlled, it can be realized...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More