Method of mfg. integrated circuit with shallow junction

A technology of integrated circuits and shallow junctions, which can be used in circuits, semiconductor/solid-state device manufacturing, electrical components, etc., and can solve problems such as increasing doping concentration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

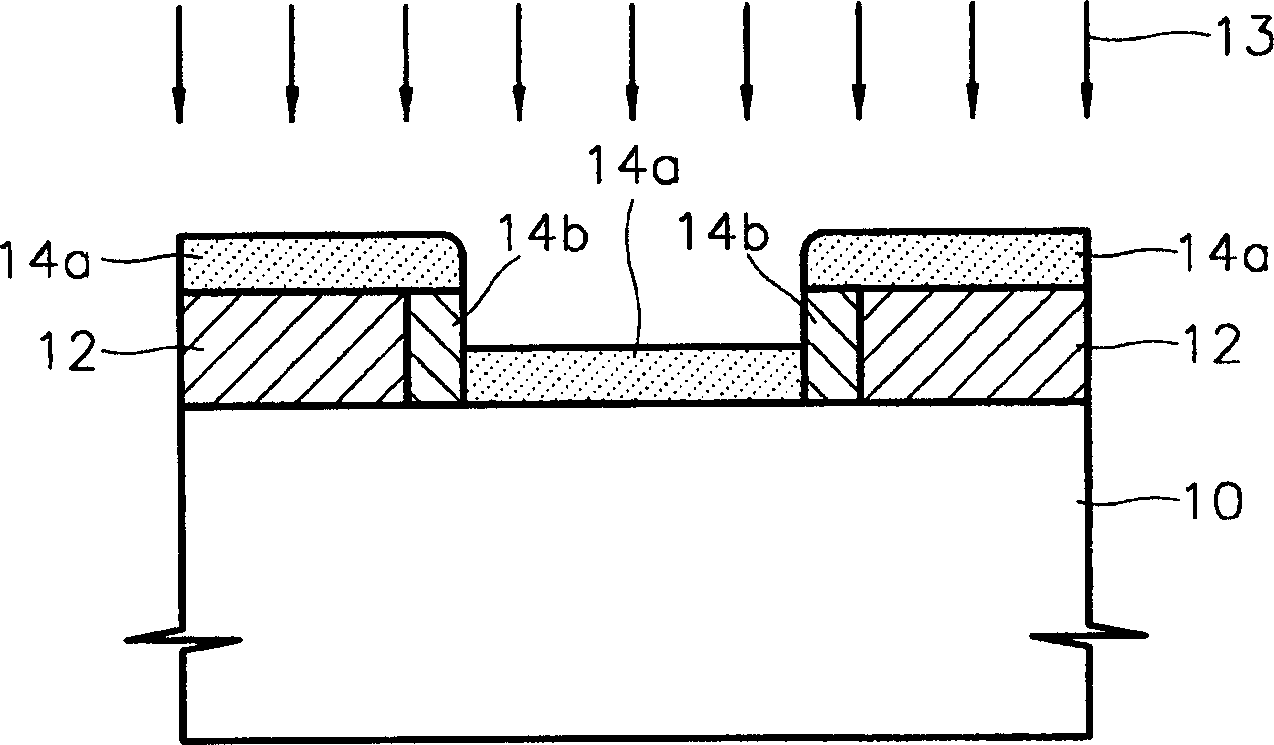

[0018] Hereinafter, embodiments of the present invention will be described in detail with reference to the accompanying drawings. However, the embodiments of the present invention can be modified into various other forms, and the scope of the present invention is not necessarily limited to these embodiments. Moreover, these embodiments are provided to more fully explain the present invention to those of ordinary skill in the art. In the drawings, the thickness of layers or regions are exaggerated for clarity. Like reference numerals in the figures represent the same parts. Also, when it is written that a layer is formed "on" another layer or substrate, the layer may be formed directly on the other layer or substrate, or the other layer may be interposed therebetween.

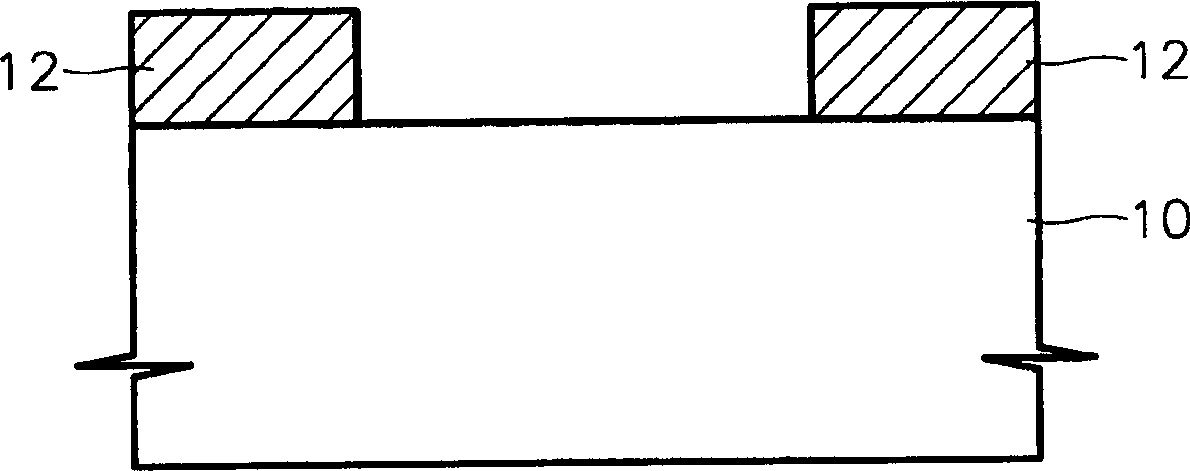

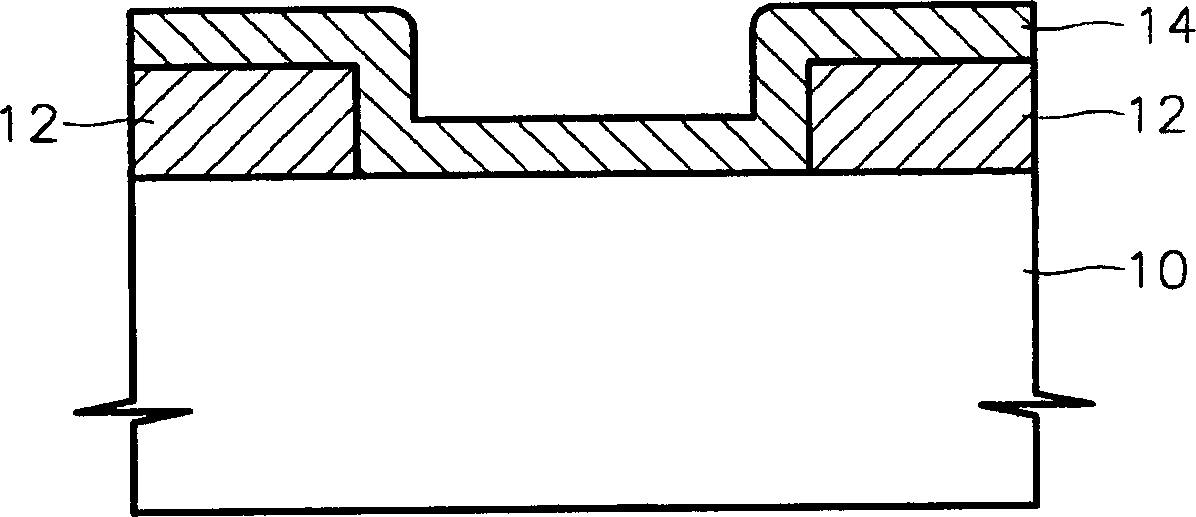

[0019] Figures 1 to 4 is a cross-sectional view illustrating a method of manufacturing an integrated circuit having a shallow junction according to a first embodiment of the present invention. see figure 1...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Doping concentration | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More