Binary adder circuit and method for producing carry logical circuit used by it

A binary adder and carry logic technology, which is applied in the calculation using the number system, the calculation using the contact device, the calculation using the non-contact manufacturing equipment, etc. Power Sensitivity, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

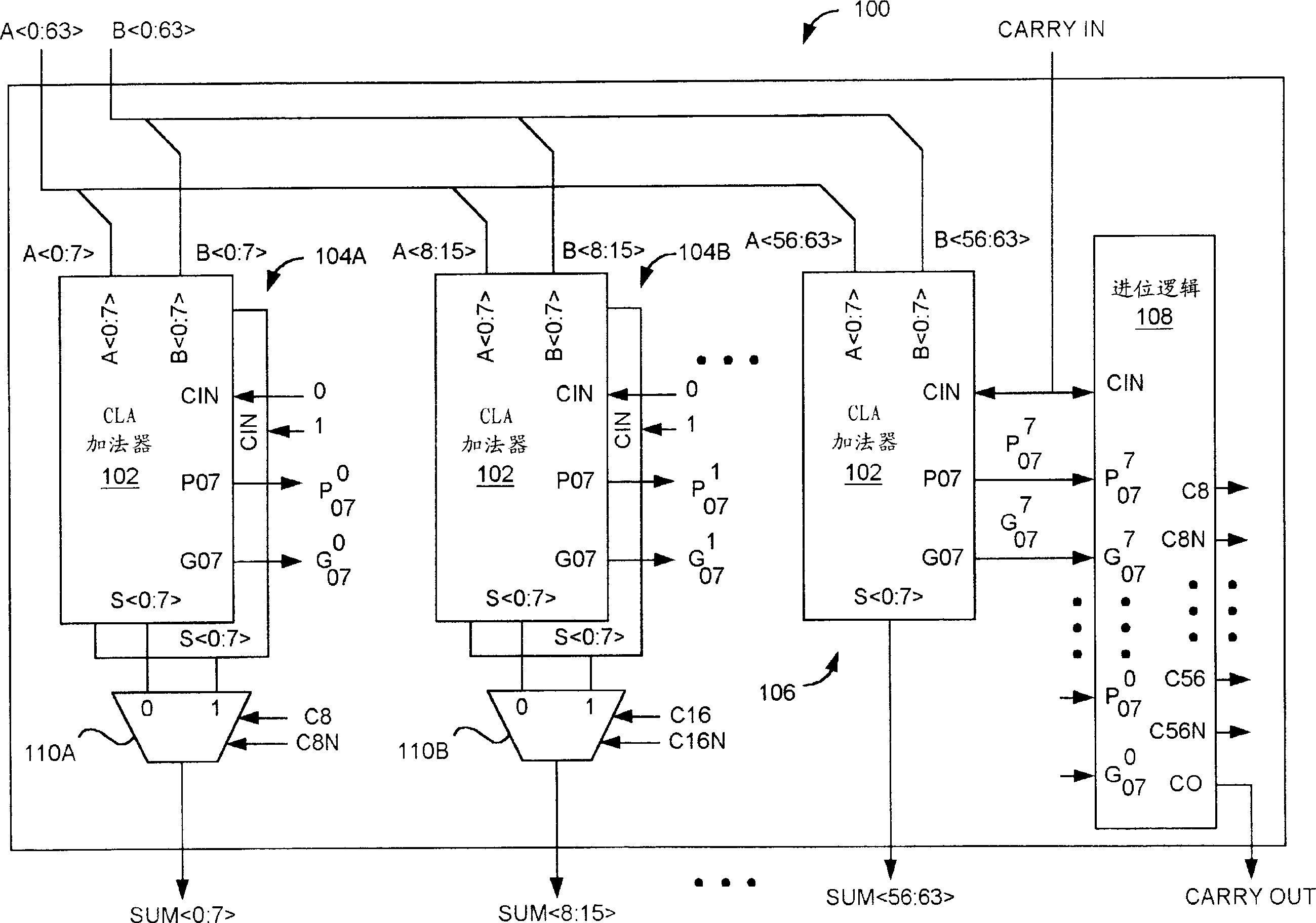

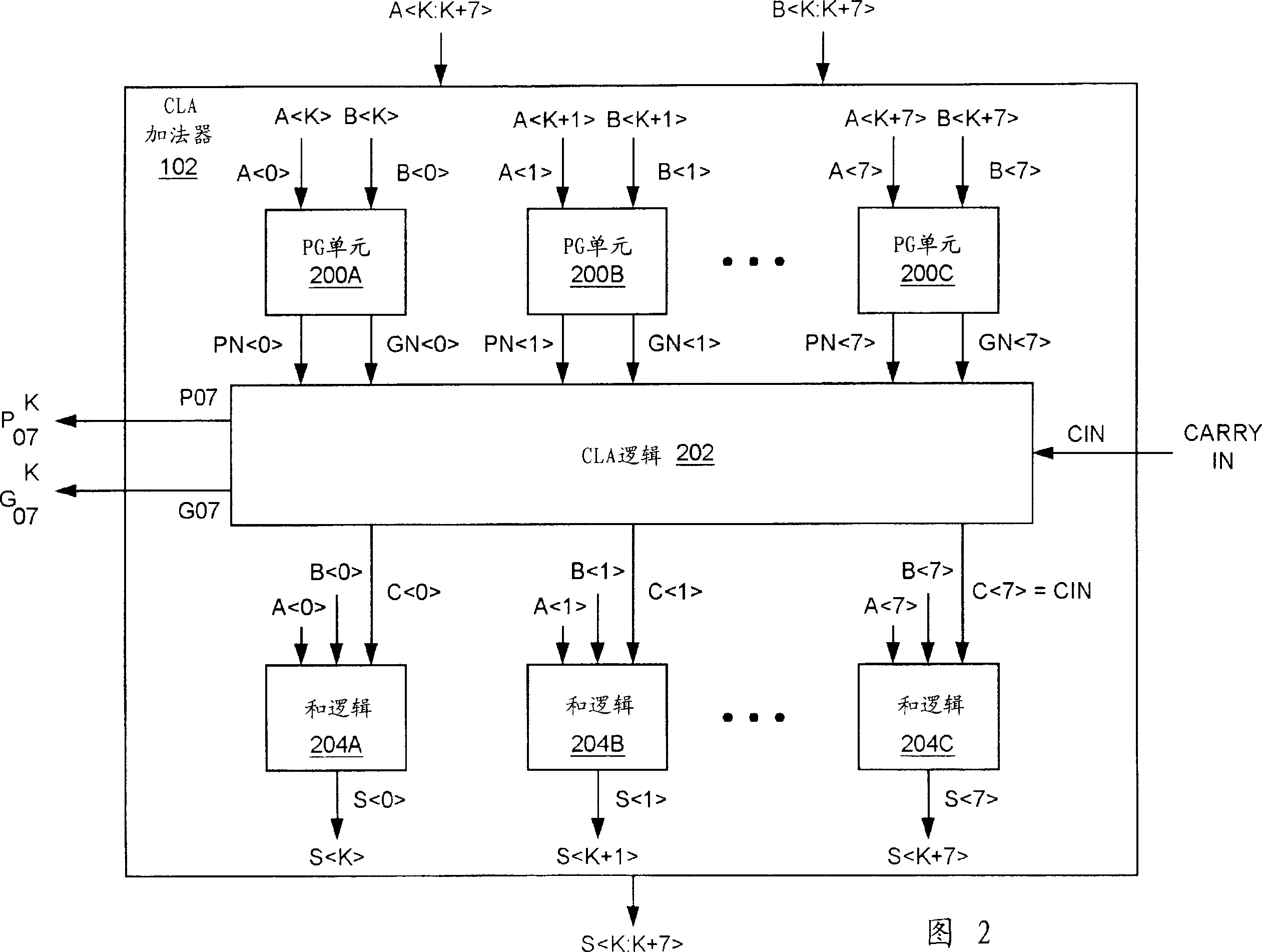

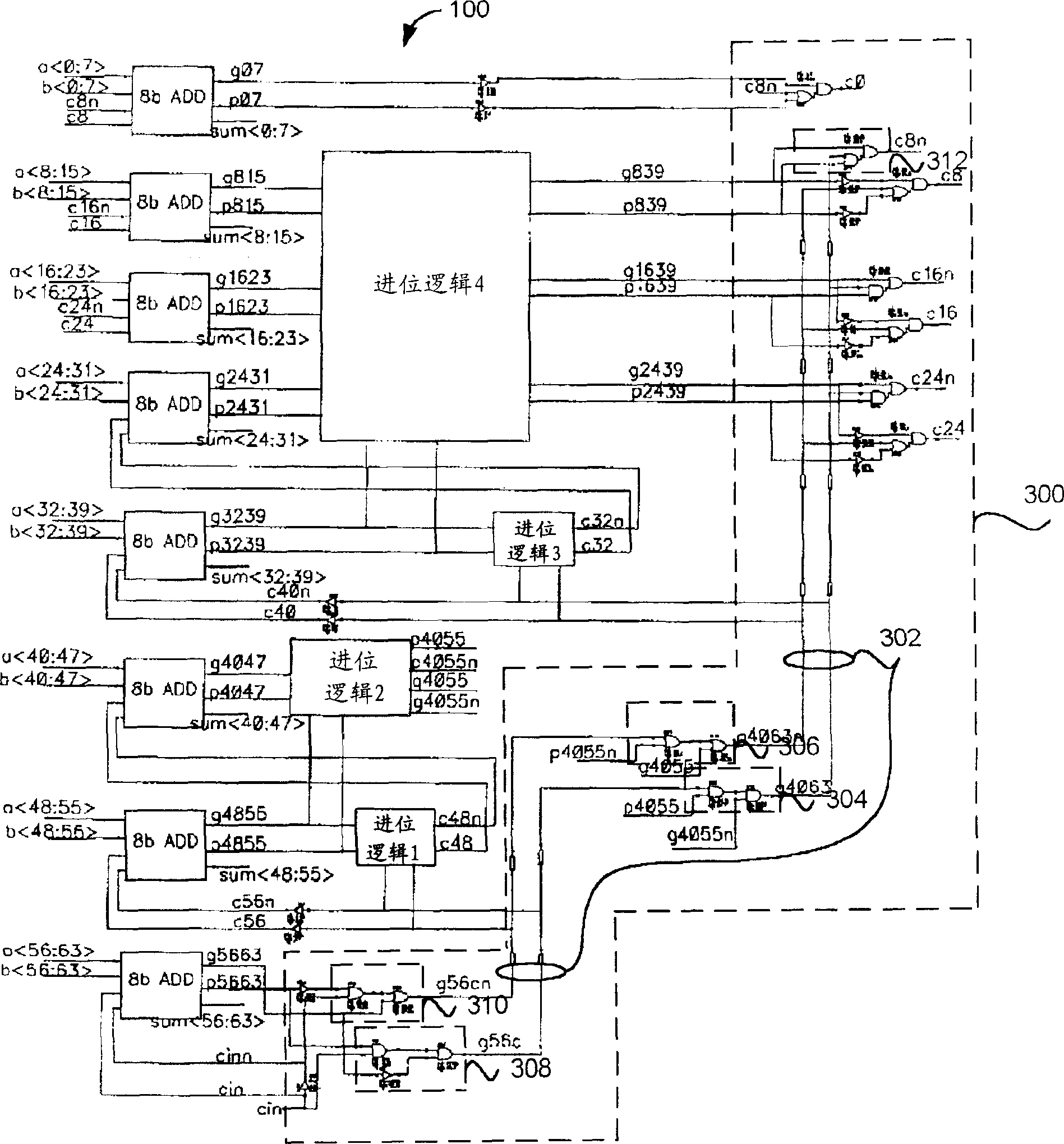

Embodiment Construction

[0023] In the following discussion, numerous specific details are set forth in order to provide a thorough understanding of the invention. However, it will be understood by those of ordinary skill in the art that the present invention may be practiced without these specific details. In other instances, well-known elements have been shown in schematic or block diagram form in order to prevent the invention from being obscured in unnecessary detail. In addition, details related to network communications, electromagnetic signal technology, etc. are mostly omitted, since these details are not considered necessary for a full understanding of the present invention, but also can be understood by one of ordinary skill in the relevant art.

[0024] It should also be noted that unless otherwise indicated, all functions described herein may be performed in hardware, software or a combination thereof. However, in a preferred embodiment, unless otherwise indicated, these functions are per...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More