Manufacturing method of gate pole structure with metal layer lateral surface part removed

A manufacturing method and metal layer technology, applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve problems such as adverse effects on electrical properties and deterioration of the overall structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

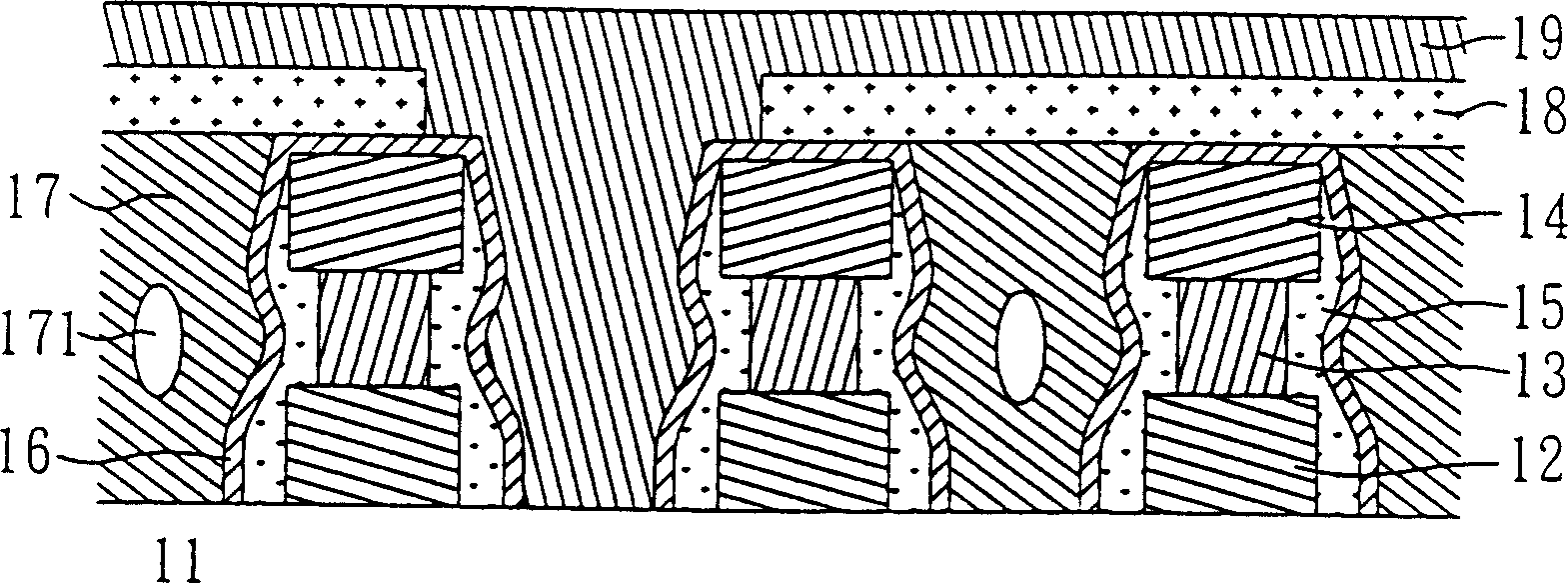

Embodiment Construction

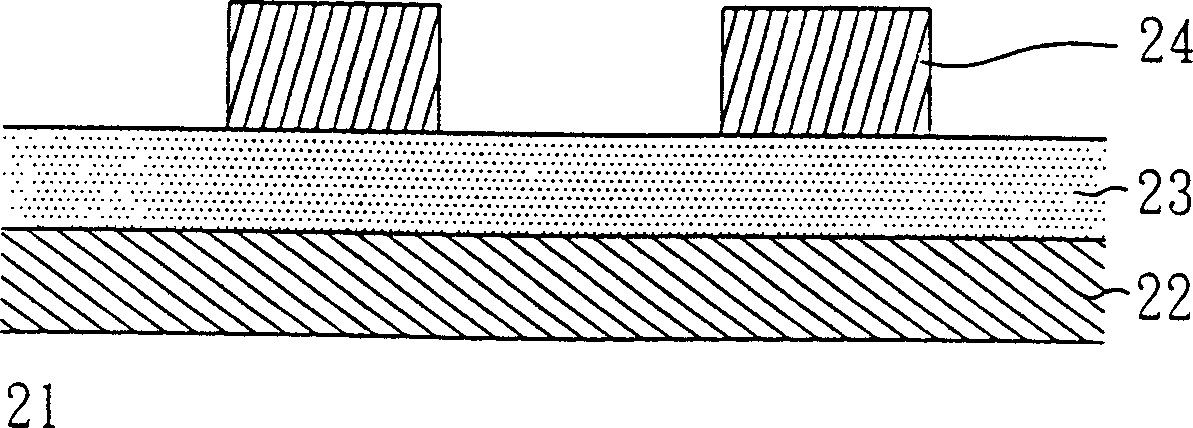

[0026] according to Figures 2a to 2g The schematic cross-sectional views of each step of the method of the present invention are shown in further detail below.

[0027] At Figure 2a In this method, a conductive layer 22 usually made of polysilicon (Poly-Si) is formed on a substrate 21 usually made of silicon by, for example, deposition, and a metal usually made of tungsten silicide (WSi) is formed on the conductive layer 22 by, for example, deposited. layer 23 , a protective layer 24 usually made of silicon nitride (SiN) is formed on the metal layer 23 by depositing and etching predetermined gate patterns, wherein each gate pattern has exposed top and side surfaces.

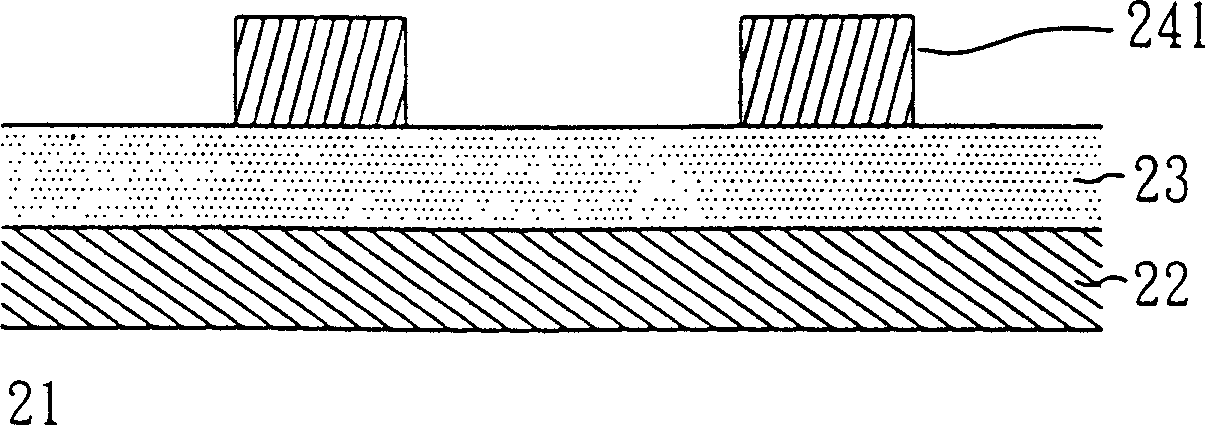

[0028] Then, the top surface and the side surface of the protection layer 24 can be partially removed by, for example, wet etching to form the gate protection layer 241, such as Figure 2b As shown, the removed side surface portion is preferably less than 20%, in order to reduce the impact on the gate electri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More