Dynamic voltage mode phase interpolation circuit suitable to phase locked loop of each annular oscillation

A technology of phase interpolation and dynamic voltage, applied in automatic power control, electrical components, etc., can solve problems such as wasting chip area and increasing total power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] Attached below Figure 1-8 The present invention is described in detail.

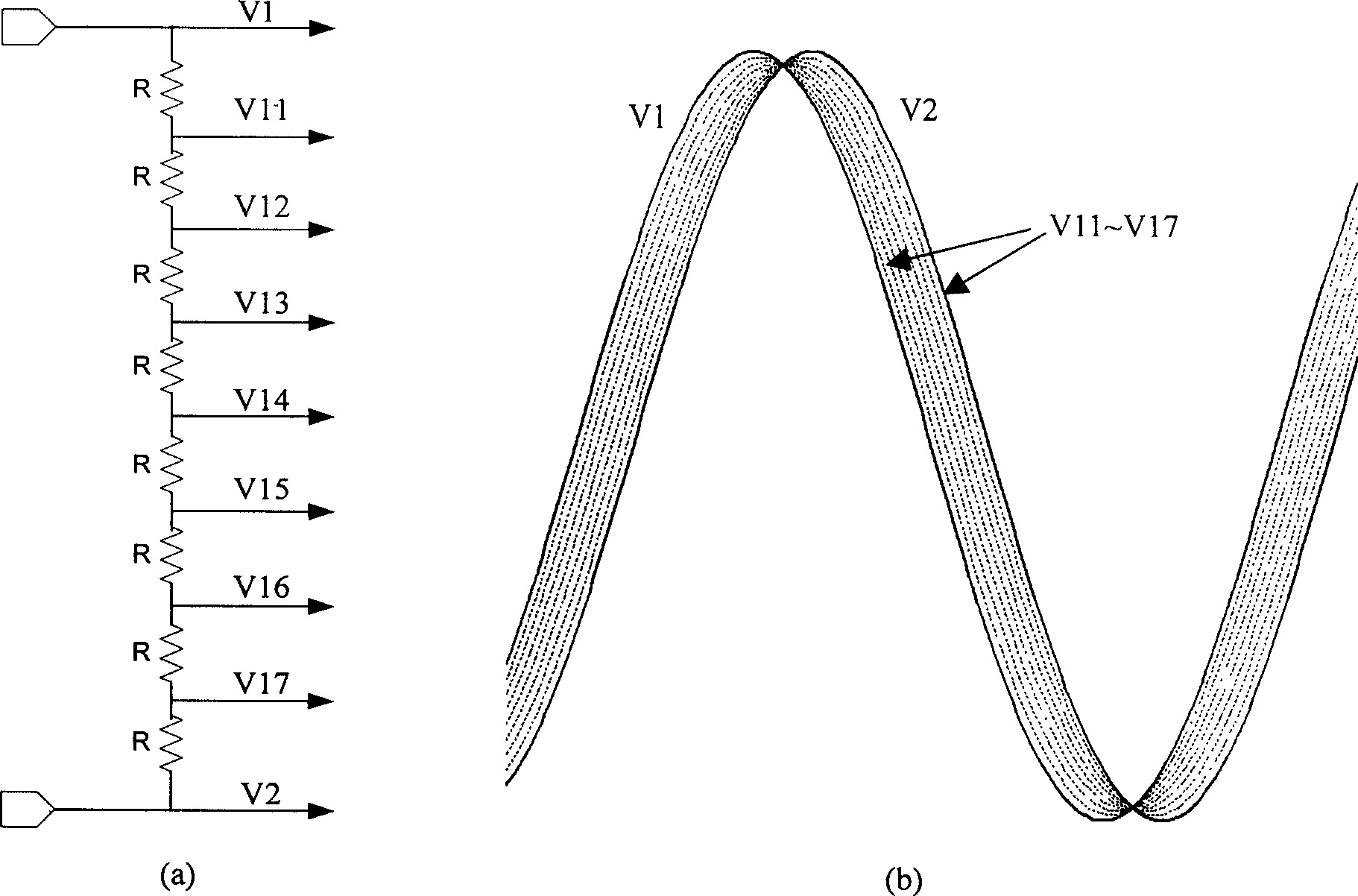

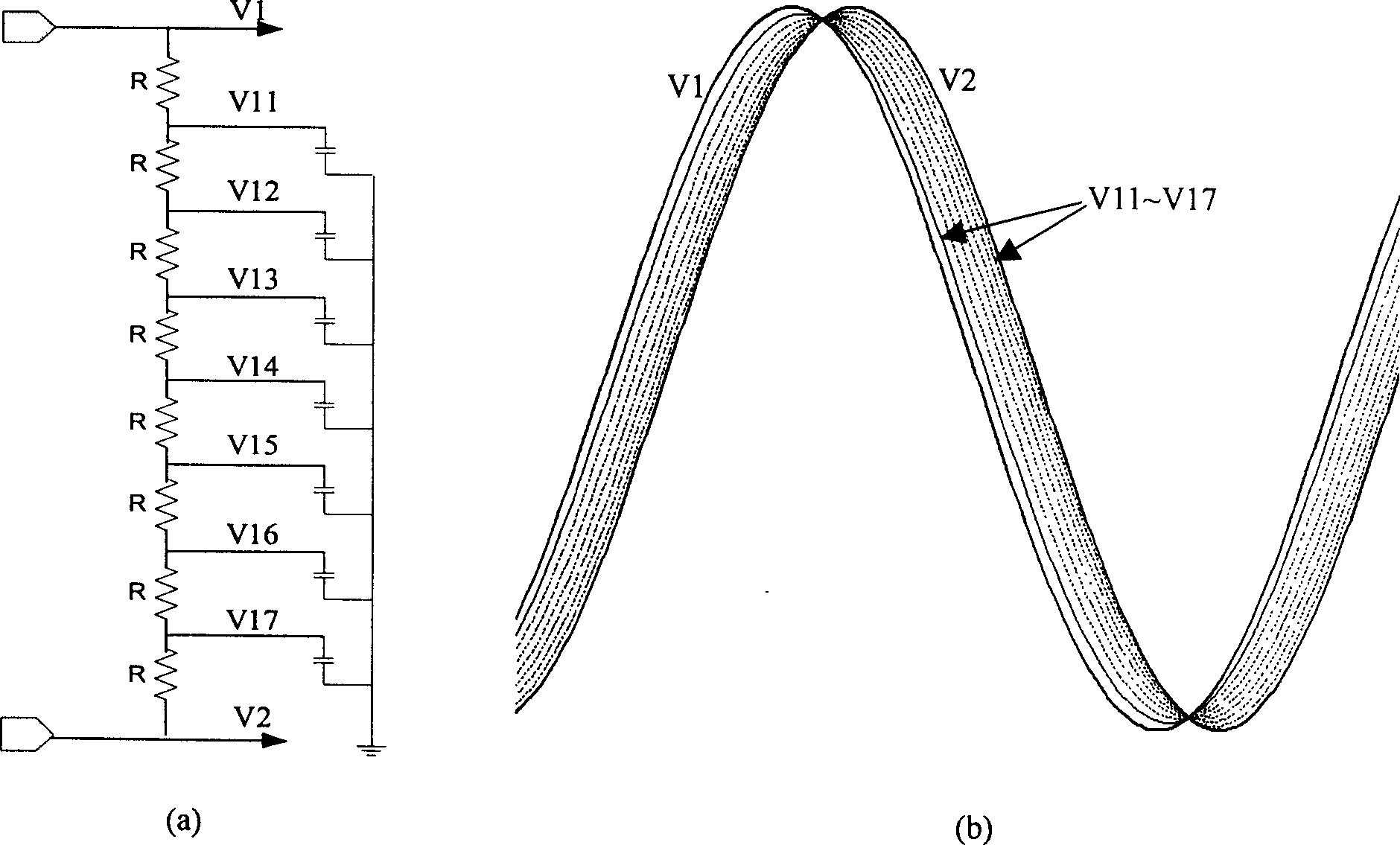

[0028] figure 1 It is a schematic diagram of the principle of resistance voltage division and a sine wave input and output waveform. What is described in the figure is the most basic and ideal situation, where the voltages V1 and V2 are used as ideal input signals, and each output is not connected to the load. At most of the time (excluding the distortion near the peak value of the waveform), the value of V1-V2 is a constant, and the current caused by the voltage difference all flows through the series voltage dividing resistor. In order to achieve the same ΔV for adjacent output voltages (which can be converted into the same time delay at the same slew rate, that is, the phase difference), the resistor string can be an average resistor, and the interpolation result has nothing to do with the absolute value of the resistor.

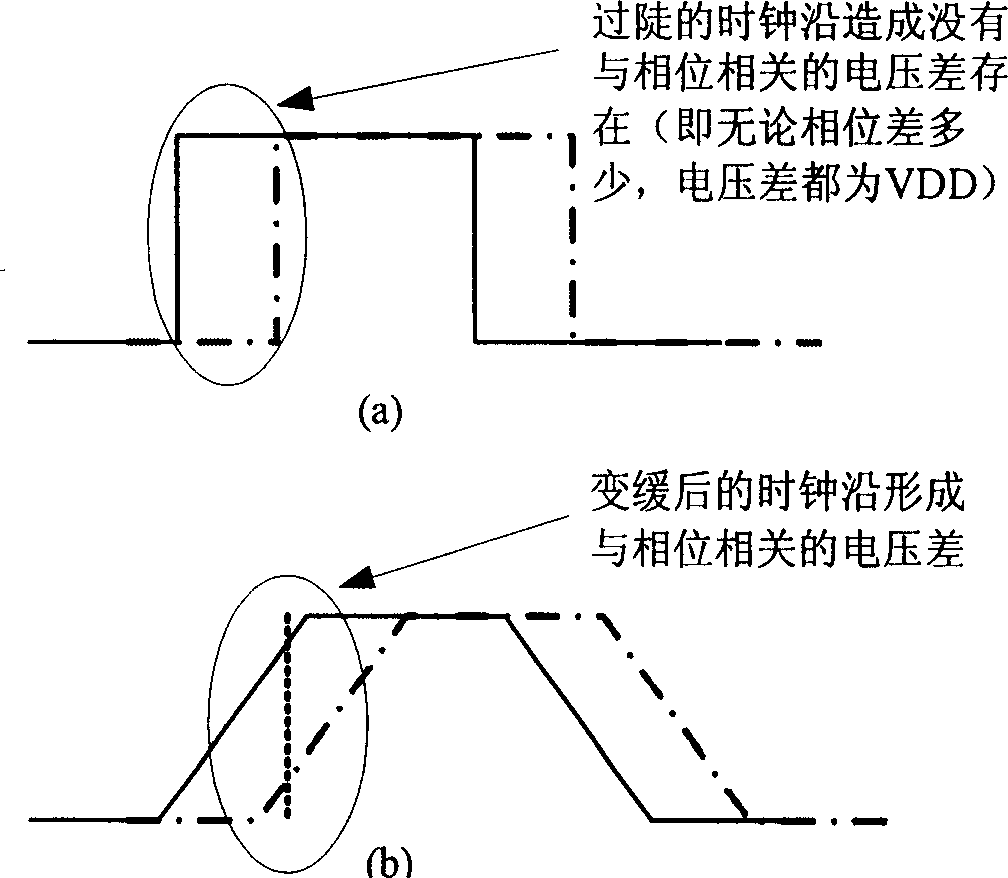

[0029] But in all applications it is impossible for the output to b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com