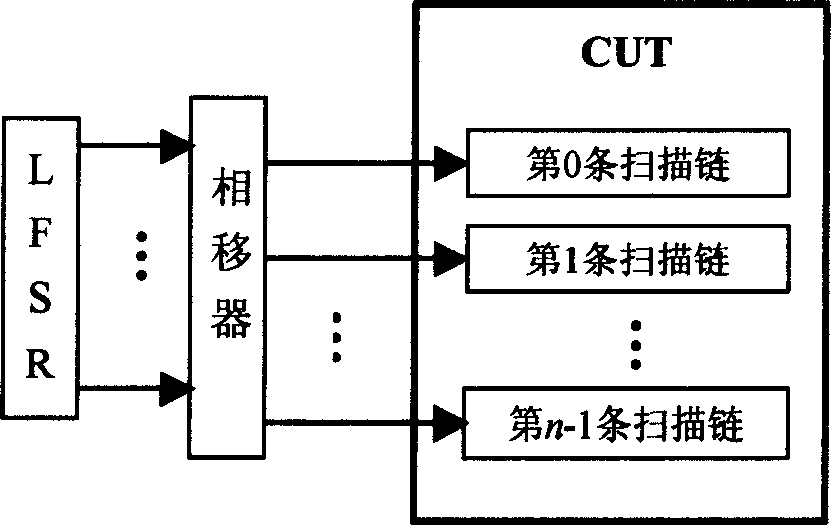

Multi-scanning chain LSI circuit test data compressing method

A large-scale integrated circuit and test data technology, applied in the direction of digital circuit test, electronic circuit test, measurement of electricity, etc., can solve the problems of large amount of test data, few chip test points, inability to perform full-speed test, etc., to reduce storage capacity , the effect of reducing the test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

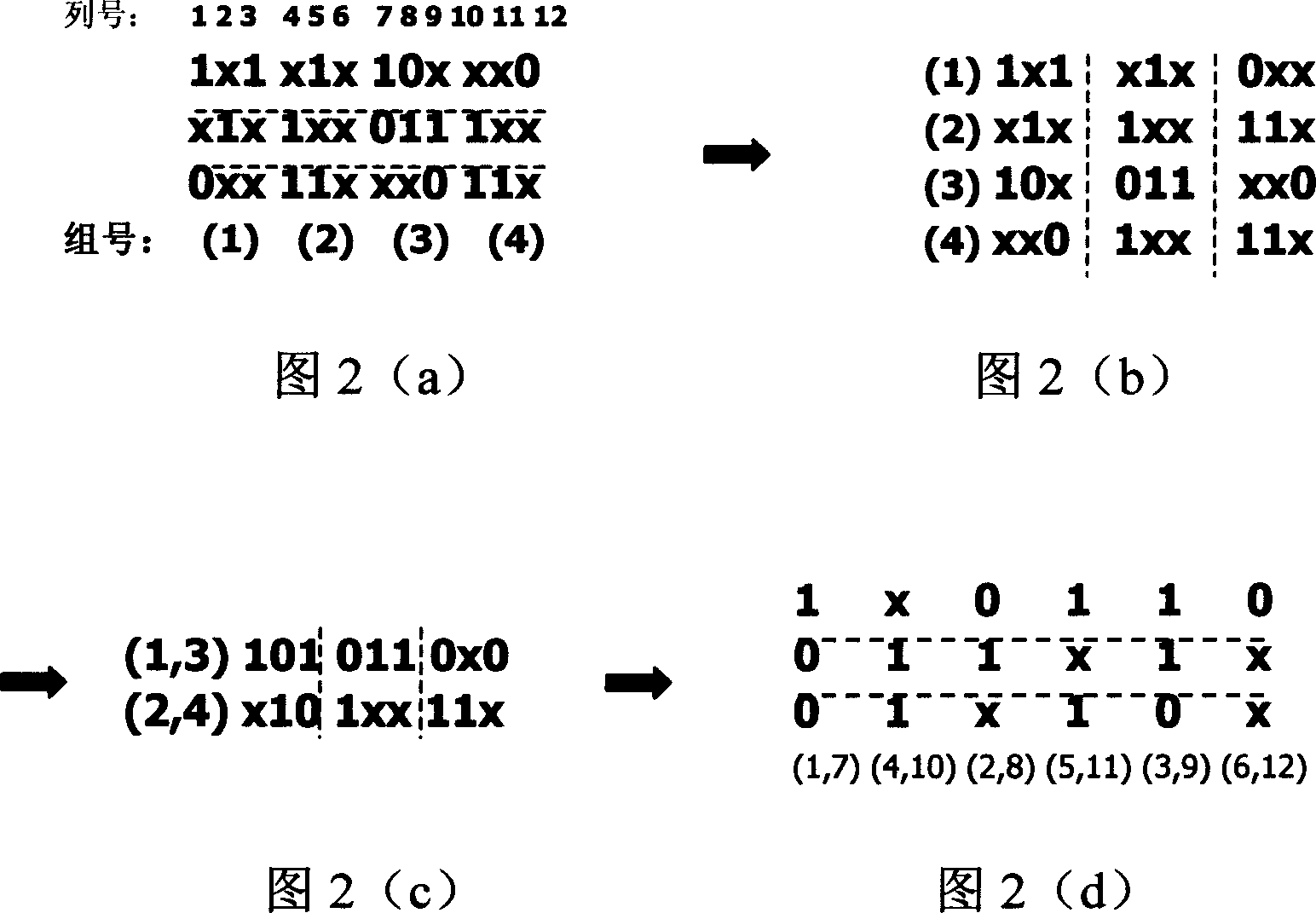

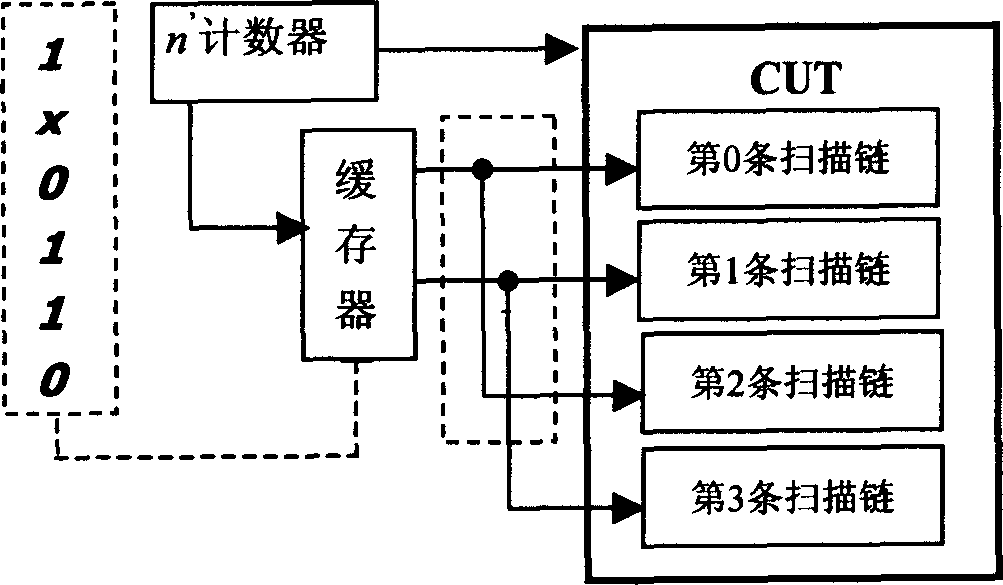

[0040] Implement the present invention and carry out as follows:

[0041] a. Perform a pseudo-random test on the circuit under test, and use fault simulation tools to determine untested faults;

[0042] b. Using the automatic test pattern generation tool ATPG to generate a certain test set T for the untested faults;

[0043] c. Simplifying the input of constraints on the test set T, the input of the constraints is to first arrange the test set T in the form of multi-scan chains and perform multi-scan chain compatible compression to obtain a compatible compression group, Then, the compatible compressed test vectors are rearranged in the form of a single scan chain, and the rearranged test set is recorded as T E ; Two test vectors are compatible if and only if their corresponding bits are the same or one is a don't care bit;

[0044] d. At the T E In, select a test vector to carry out LFSR encoding, generate the seed of LFSR, the produced LFSR seed is the test data that needs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com