Planar mono-silicon double-metal layer power device and its production

A dual-metal layer, power device technology, used in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., can solve problems such as high cost, large silicon wafer area, and unfavorable integrated circuit miniaturization, and achieve low cost, Good product quality and the effect of improving the performance of low capacitance and fast turn-on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

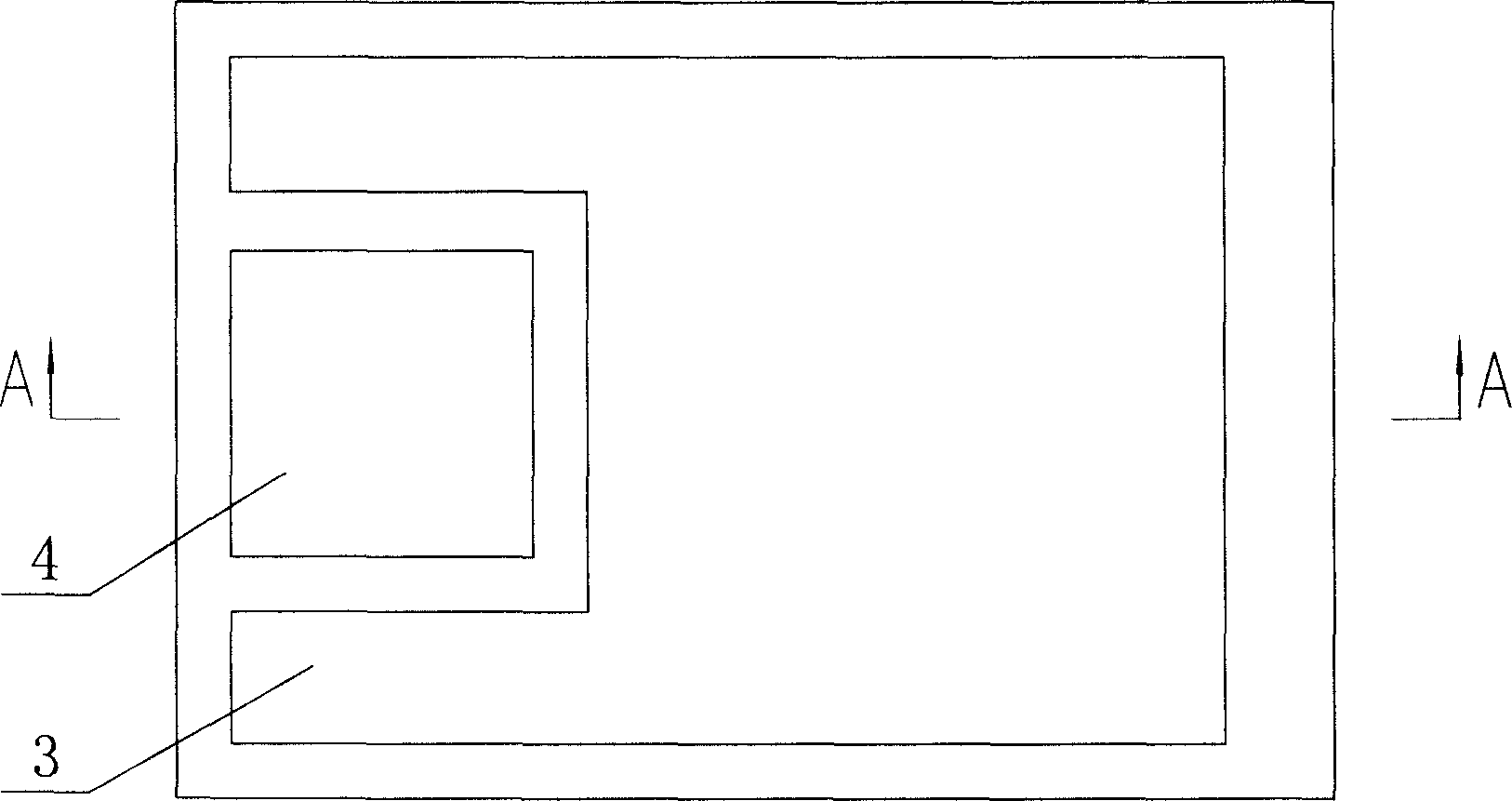

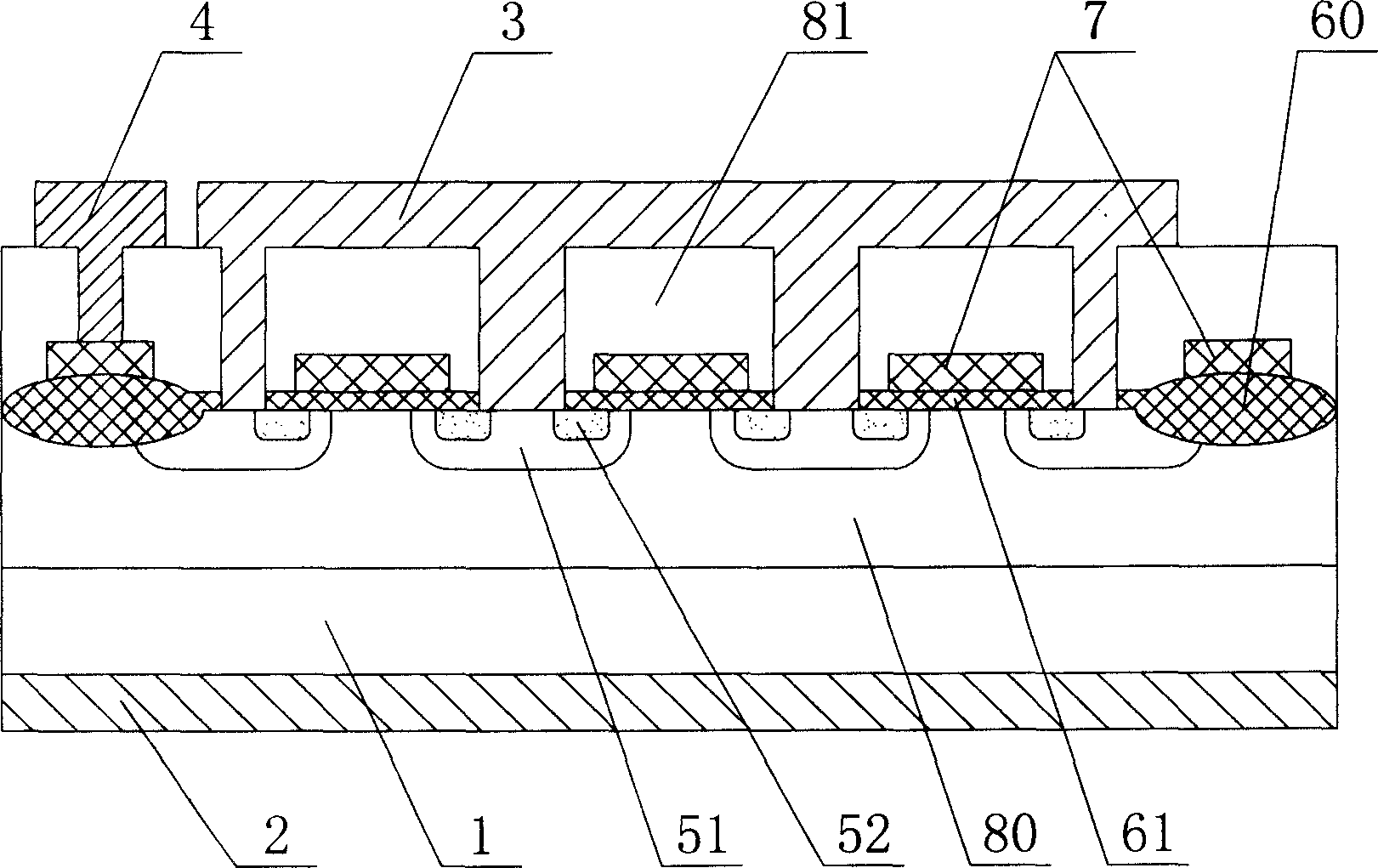

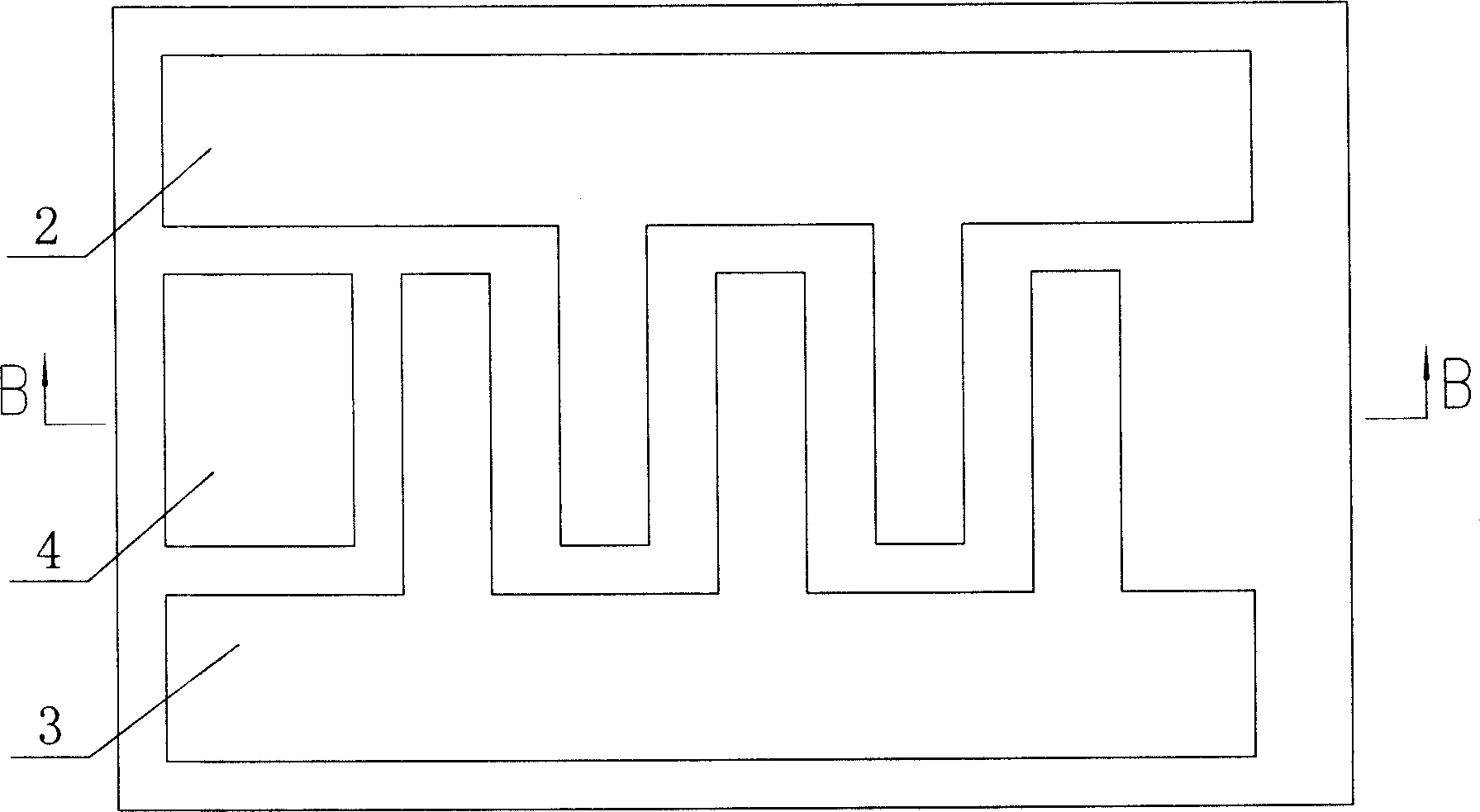

[0047] Such as Figure 5 to Figure 9 As shown, the planar single-silicon double-metal layer power device of this embodiment is an N-channel MOSFET, which includes an N-type silicon substrate 1, a P-type well region 90 formed in the silicon substrate 1, and a P-type well region 90 formed in the silicon substrate 1. The oxide layer I81 on the front side of the silicon substrate 1, the drain metal I2, source metal I3, and gate metal I4 located on the front side of the oxide layer I81, are implanted into the P+well contact region 50 in the silicon substrate 1 , N+ source region 52, N+ drain region 53, connecting the channel region 65 between the source region 52 and the drain region 53, growing on the gate oxide layer I60 and gate oxide layer II61 on the front side of the silicon substrate 1, The polysilicon gate 7 located on the gate oxide layer I60 and the gate oxide layer II61, the polysilicon gate 7 is distributed in stripes, and there are five stripes and one annular through ...

Embodiment 2

[0061] Such as Figure 10 ~ Figure 12 As shown, the planar single-silicon double-metal layer power device of this embodiment is a P-channel MOSFET. The through-holes I83 through which the metal I2 and the source metal I3 are in contact with the silicon substrate 1 are also distributed in grid-like intervals. The silicon substrate 1 is an N-type substrate, the well region 90 is an N-type well region, the well contact region 50 is an N+ well contact region, the source region 52 is a P+ source region, and the drain region 53 It is the P+ drain area. The drain metal I2, the source metal I3, the gate metal I4, the drain metal II2', the source metal II3', and the gate metal II4' are copper. Other features are the same as in Embodiment 1.

[0062] The difference between the manufacturing method of the planar single-silicon double-metal layer power device of this embodiment and the first embodiment is that:

[0063] Step (b) Forming the well region: Implanting phosphorus N-type do...

Embodiment 3

[0069] The planar single-silicon double-metal layer power device of this embodiment is an N-channel MOSFET, and it differs from Embodiment 1 in that the gate metal II4' is connected to the gate metal II4' through another through hole II84. Metal I4 is connected and connected to other circuits without forming a pad. The silicon substrate 1 is a P-type substrate, the well region 90 is a P-type well region, the well contact region 50 is a P+ well contact region, the source region 52 is an N+ source region, and the drain region 53 It is the N+ drain region. The drain metal I2, the source metal I3, the gate metal I4, the drain metal II2', the source metal II3', and the gate metal II4' are silicon aluminum alloys. Other features are the same as in Embodiment 1.

[0070] The difference between the manufacturing method of the planar single-silicon double-metal layer power device of this embodiment and the first embodiment is that:

[0071] Step (b) forming a well region: inject bor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More