Chip and packaging structure

A packaging structure and chip technology, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problems of increasing the stress of packaging colloid

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

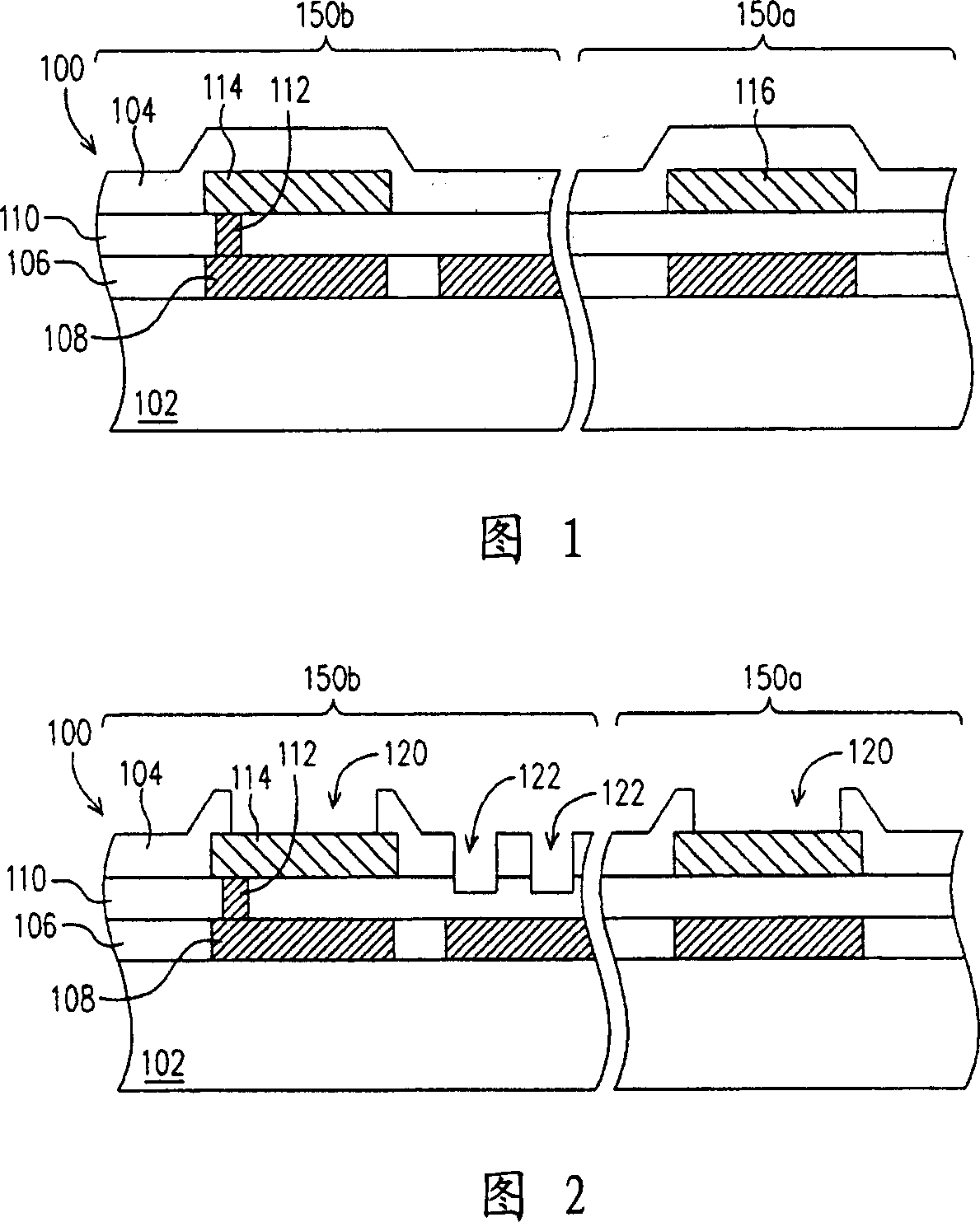

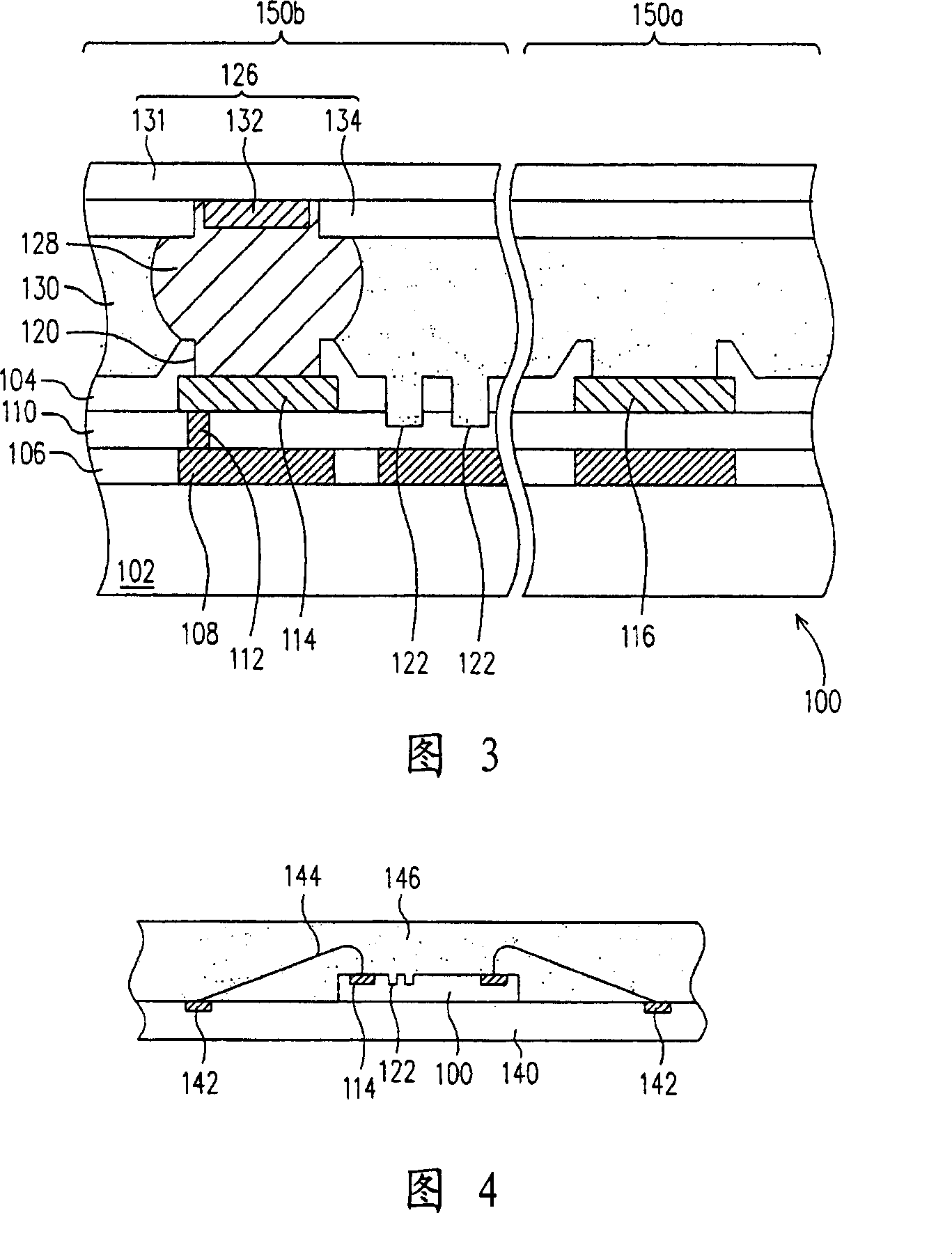

[0041] FIG. 1 to FIG. 2 are cross-sectional views of a manufacturing method of a chip according to an embodiment of the present invention. Referring to FIG. 1 , a chip 100 is provided first. The chip 100 has a substrate 102 and a passivation 104 on the substrate 102 . For the convenience of illustration, FIG. 1 to FIG. 2 only show part of the substrate 102, and the part of the substrate 102 is also configured with a dielectric layer 106, a metal layer 108, a dielectric layer 110, a via (Via) 112, and a solder pad. 114 and fuse pad 116. The material of the dielectric layer 106 is, for example, silicon oxide. The metal layer 108 is disposed in the dielectric layer 106 . The metal layer 108 is, for example, an interconnection wire, and its material is, for example, aluminum or copper. The dielectric layer 110 is disposed on the dielectric layer 106 . The material of the dielectric layer 110 is, for example, silicon oxide. The via window 112 is disposed in the dielectric laye...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More