Semiconductor integrated circuit

a technology of integrated circuits and semiconductors, applied in the direction of vessel construction, pulse technique, separation process, etc., can solve the problems of small voltage drop occurring in a resistive component of the power line, affecting the delay of the signal, and increasing the load of the design work, so as to reduce the load of layout design, the degree of freedom of arrangement of the power switch cells, and the effect of suppressing the voltage drop of the power due to the power switch cells

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

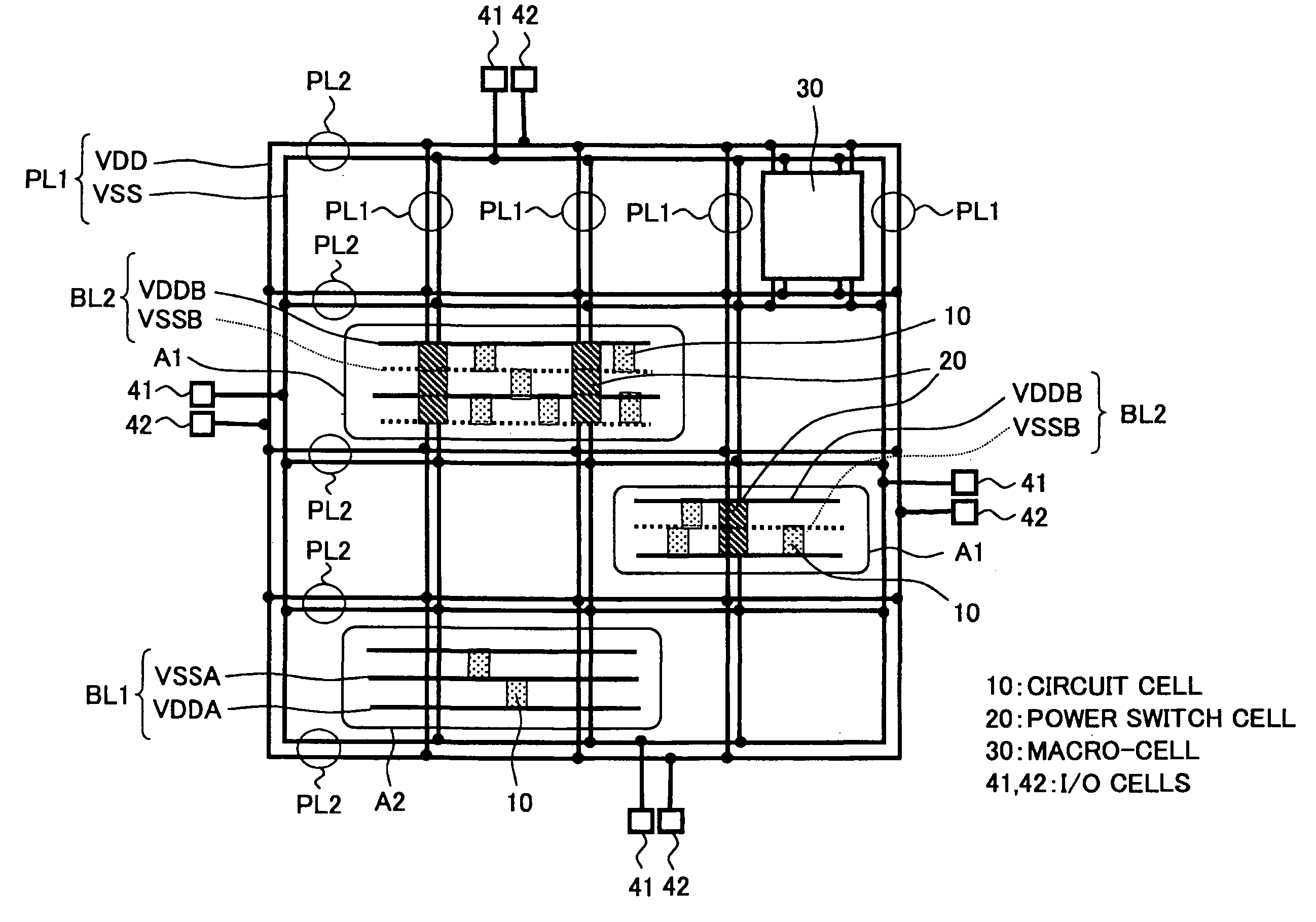

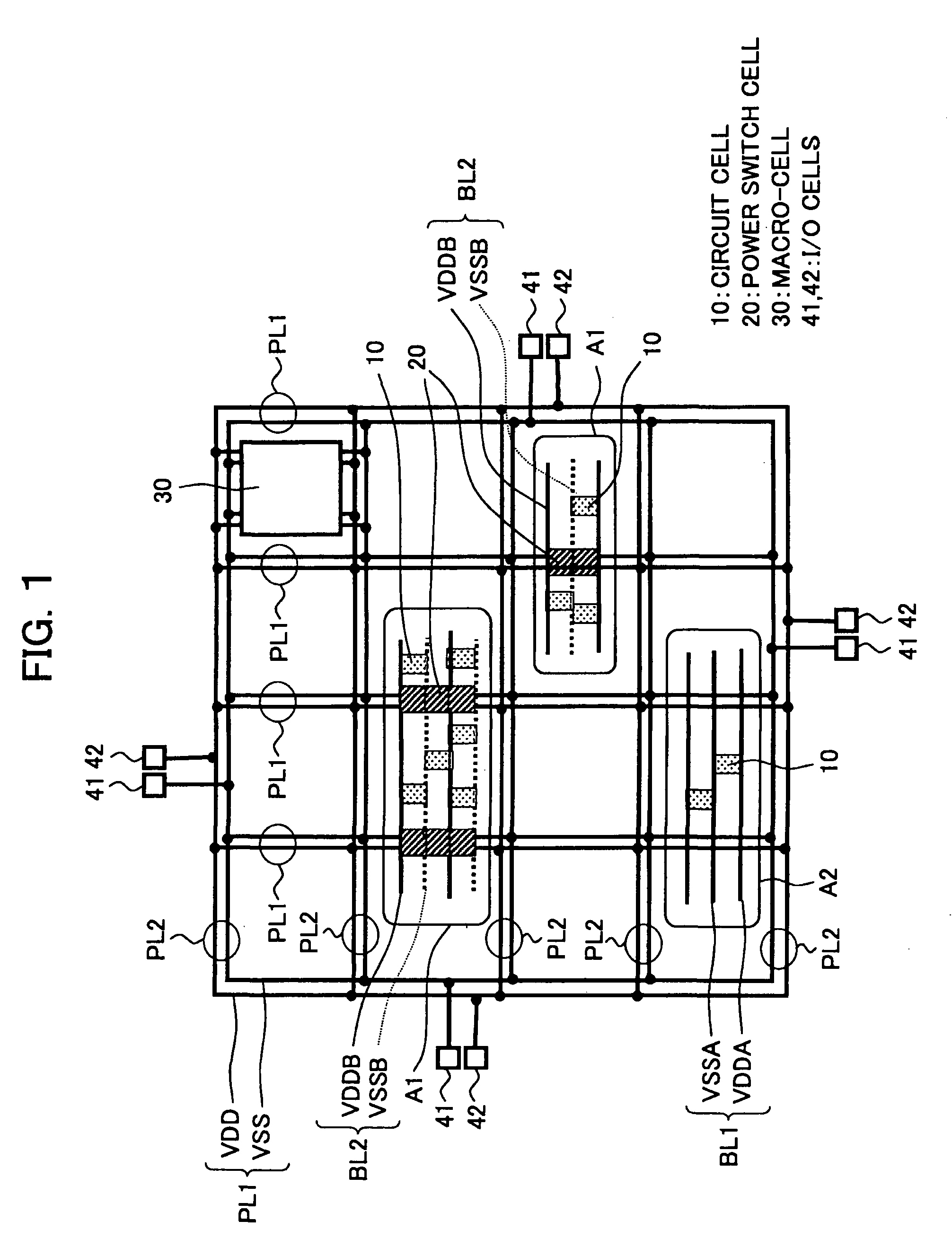

[0047]FIG. 1 is a view of an example of the configuration of a semiconductor integrated circuit according to a first embodiment of the present invention. In the figure, interconnect lines relating to the power and circuit cells connected to them are schematically illustrated.

[0048] The semiconductor integrated circuit shown in FIG. 1 has a plurality of groups of power lines PL1, a plurality of groups of power lines PL2, a plurality of groups of branch lines BL1 and BL2, a plurality of circuit cells 10, a plurality of power switch cells 20, a circuit block 30, and a plurality of power input cells 41 and 42.

[0049] Note that the groups of power lines PL1 are embodiments of the groups of power lines of the present invention, the groups of branch lines BL2 are embodiments of the groups of branch lines of the present invention, the circuit cells 10 are embodiments of the circuit cells of the present invention, and the power switch cells 20 are embodiments of the power switch cells of th...

second embodiment

[0070] Next, a second embodiment of the present invention will be explained.

[0071] The semiconductor integrated circuit according to the second embodiment shows the configurations of the power switch cells and circuit cells and the structures of the groups of branch lines connecting them in more detail than the semiconductor integrated circuit according to the first embodiment. The overall configuration such as the arrangement of the groups of power lines is the same as that of the semiconductor integrated circuit according to the first embodiment.

[0072]FIG. 4 is a view of an example of the configuration of a circuit cell 11 according to the second embodiment of the present invention. The circuit cell 11 shown in FIG. 4 has an inverter circuit configured as a serial circuit of a p-type MOS transistor Qp1 and an n-type MOS transistor Qn1 and has interconnect lines L111 and L112 supplying power to this inverter circuit. Note that while FIG. 4 shows an inverter circuit cell as one ex...

third embodiment

[0093] Next, a third embodiment of the present invention will be explained.

[0094] The semiconductor integrated circuit according to the third embodiment is obtained by changing parts of the configurations of the power switch cells and the interconnect line structures in the second embodiment explained above. The overall configuration such as the arrangement of the groups of power lines and the configuration of the circuit cells are the same as those of the semiconductor integrated circuits according to the first and second embodiments.

[0095]FIG. 7 is a view of an example of the configuration of a power switch cell 22 according to the third embodiment of the present invention. The power switch cell 22 has an n-type MOS transistor Qn3 and interconnect lines L221 to L223. The n-type MOS transistor Qn3 is an embodiment of the switch circuit of the present invention, the interconnect line L221 is an embodiment of the third interconnect line of the present invention, and the interconnec...

PUM

| Property | Measurement | Unit |

|---|---|---|

| power | aaaaa | aaaaa |

| angle | aaaaa | aaaaa |

| area | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More