Relative dynamic skew compensation of parallel data lines

a parallel data line and relative dynamic technology, applied in the field of can solve the problems of requiring significant re-architecting and design effort, unable to easily increase the bandwidth of serial links from the original implementation, and typically not the case for high-speed parallel data links, so as to reduce power consumption and reduce parts coun

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0061] In accordance with the various embodiments of the present invention and referring now to the figures, wherein like reference numerals identify like elements of the various embodiments of the invention, one can effectively perform relative dynamic skew compensation of parallel data lines. Additionally, the hardware implementation of the deskewing circuit in accordance with the present invention includes a delay line having a reduced parts count and reduced power consumption, and the deskewing circuit is process independent and is scalable.

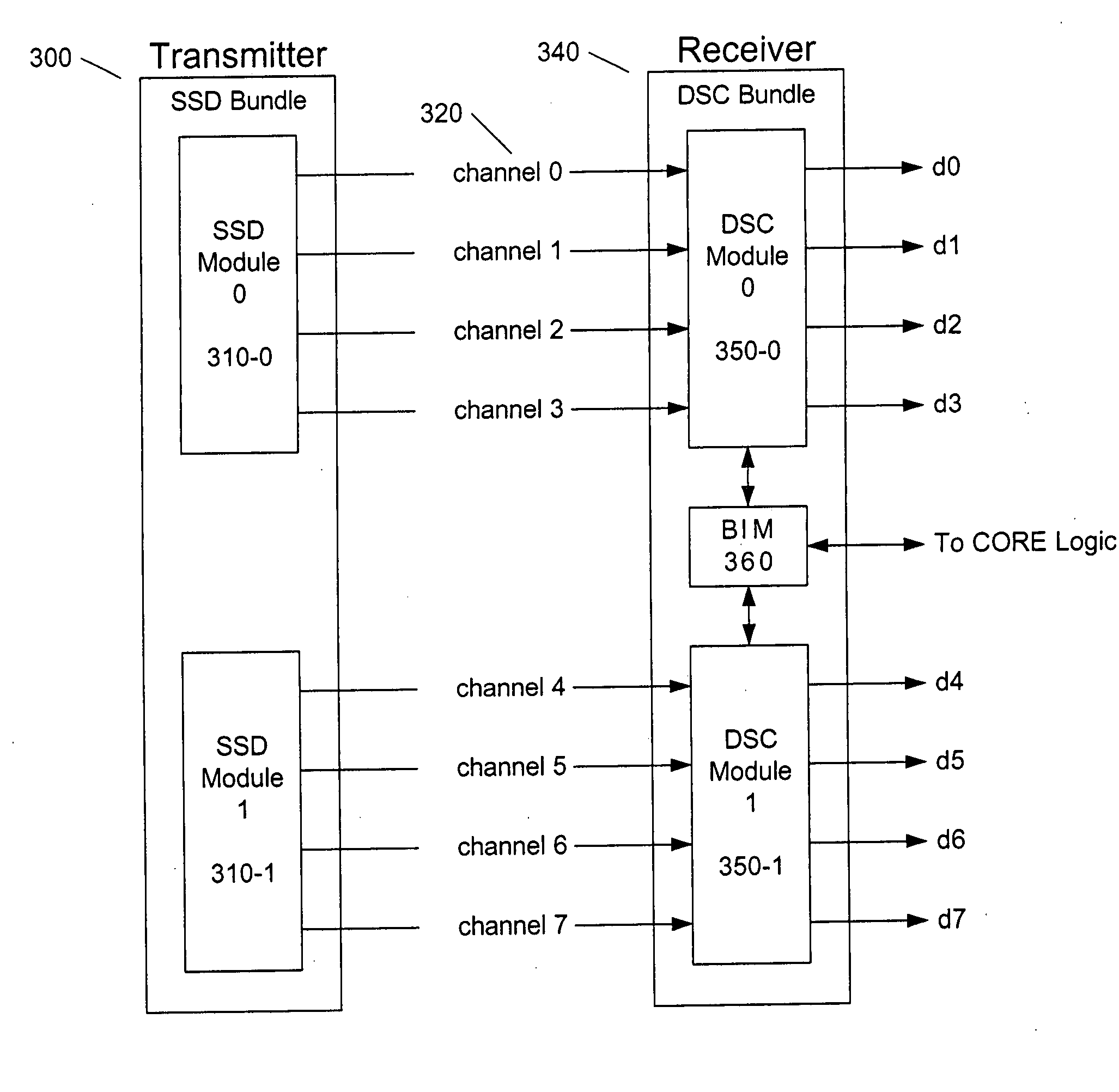

[0062] A preferred embodiment of the deskewing system in accordance with the present invention is shown in FIG. 3. Generally, the link architecture and operation are as follows.

[0063] At a source node, a transmitter 300 comprised of one or more Source Synchronous Driver (SSD) Modules 310-0, 310-1, . . . 310-N drives data onto physical media, for example, optic fiber or copper ribbon cable, forming a parallel bus 320 consisting of a pluralit...

PUM

| Property | Measurement | Unit |

|---|---|---|

| time | aaaaa | aaaaa |

| phase | aaaaa | aaaaa |

| zero phase alignment | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More