High performance integrated vertical transistors and method of making the same

a vertical transistor, high-performance technology, applied in the direction of transistors, semiconductor devices, electrical equipment, etc., can solve the problems of significant degrading affecting the operation of the two devices, and affecting the performance of the npn devi

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

)

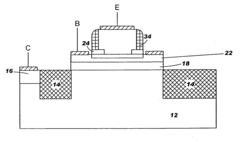

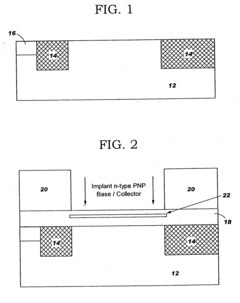

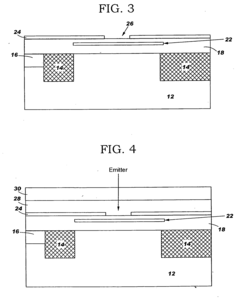

[0027] In describing the preferred embodiment of the present invention, reference will be made herein to FIGS. 1-11 of the drawings in which like numerals refer to like features of the invention.

[0028] The present invention provides a complementary bipolar transistor fabricated using a shared silicon germanium (SiGe) low temperature epitaxial (LTE) layer, wherein the epitaxially deposited raised extrinsic base layer of the NPN transistor is also used for the PNP diffused emitter layer. Both the NPN and PNP base and emitter regions are fully or partially contained in the LTE layer. The collector region of the PNP and NPN transistors may be inside the LTE layer as well, although not necessitated. An available in-situ doped arsenic base polysilicon layer is used as the vertical PNP emitter layer. The present invention utilizes advanced epitaxial techniques, such as molecular beam epitaxy (MBE) and low temperature epitaxy (LTE) by ultra high vacuum chemical vapor deposition (UHV / CVD) ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More