Phase alignment mechanism for minimizing the impact of integer-channel interference in a phase locked loop

a phase locking loop and integer channel technology, applied in the field of data communication, can solve the problems of not being able to tolerate output of pll, and achieve the effect of minimizing the impact of interferen

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

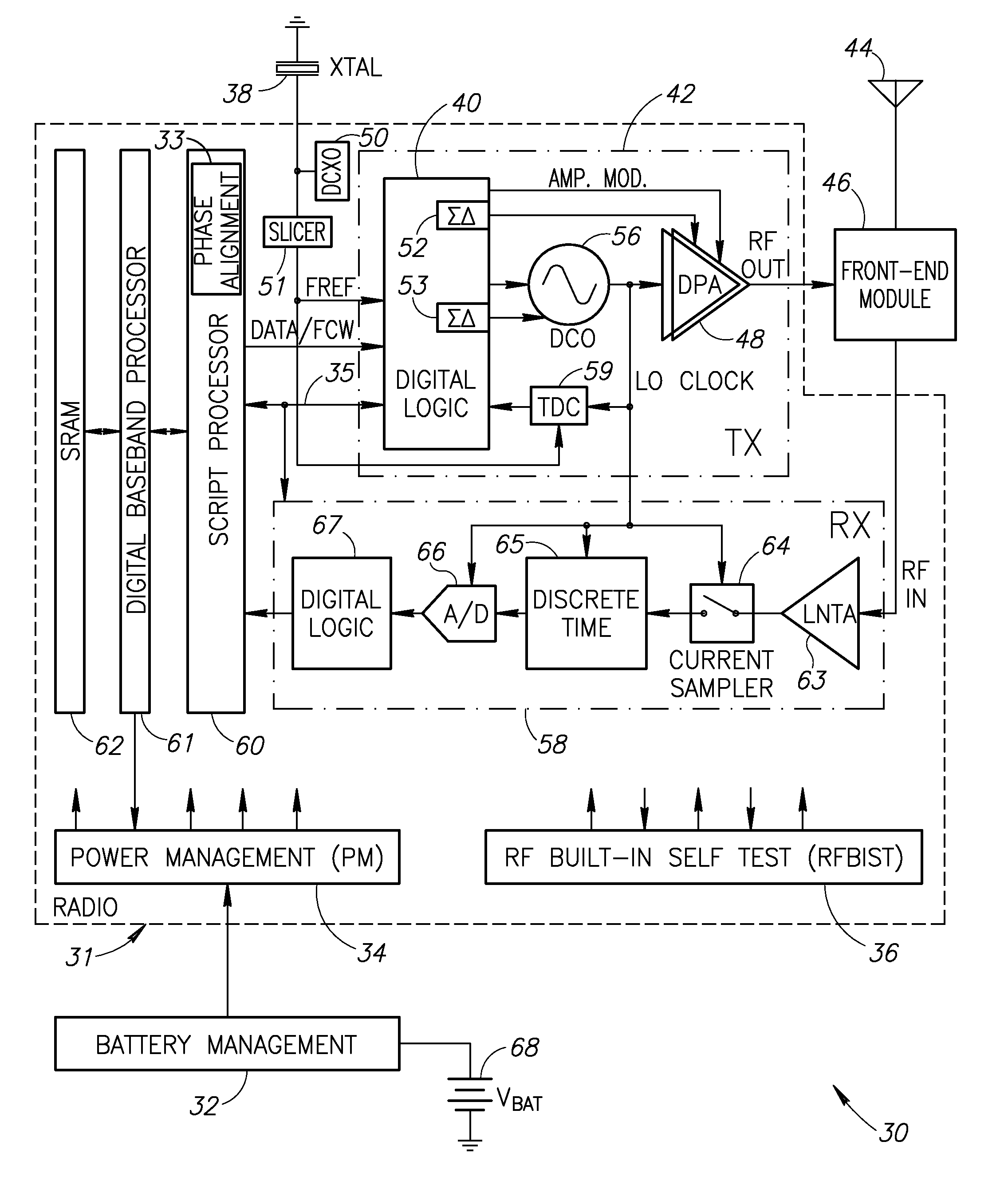

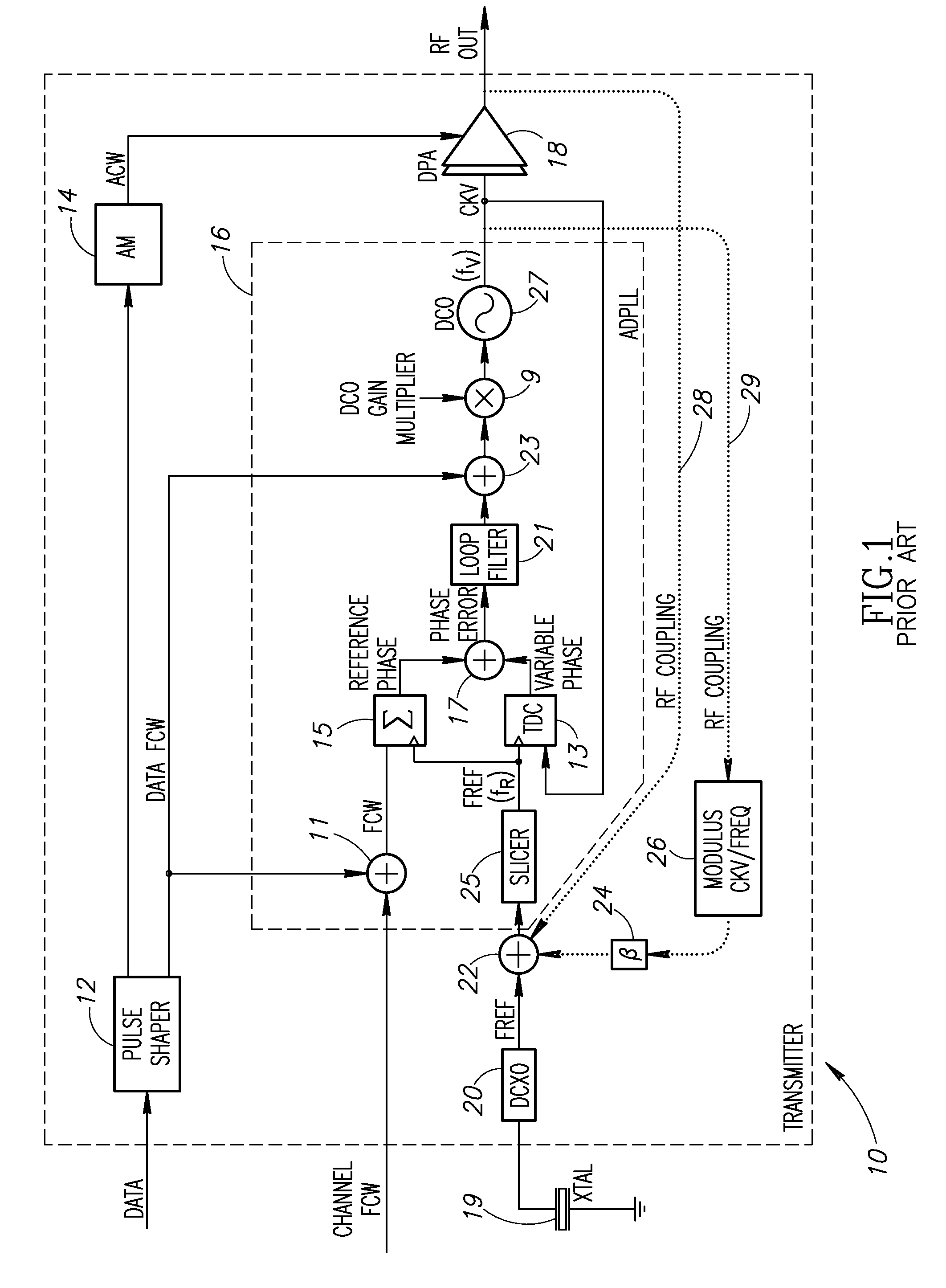

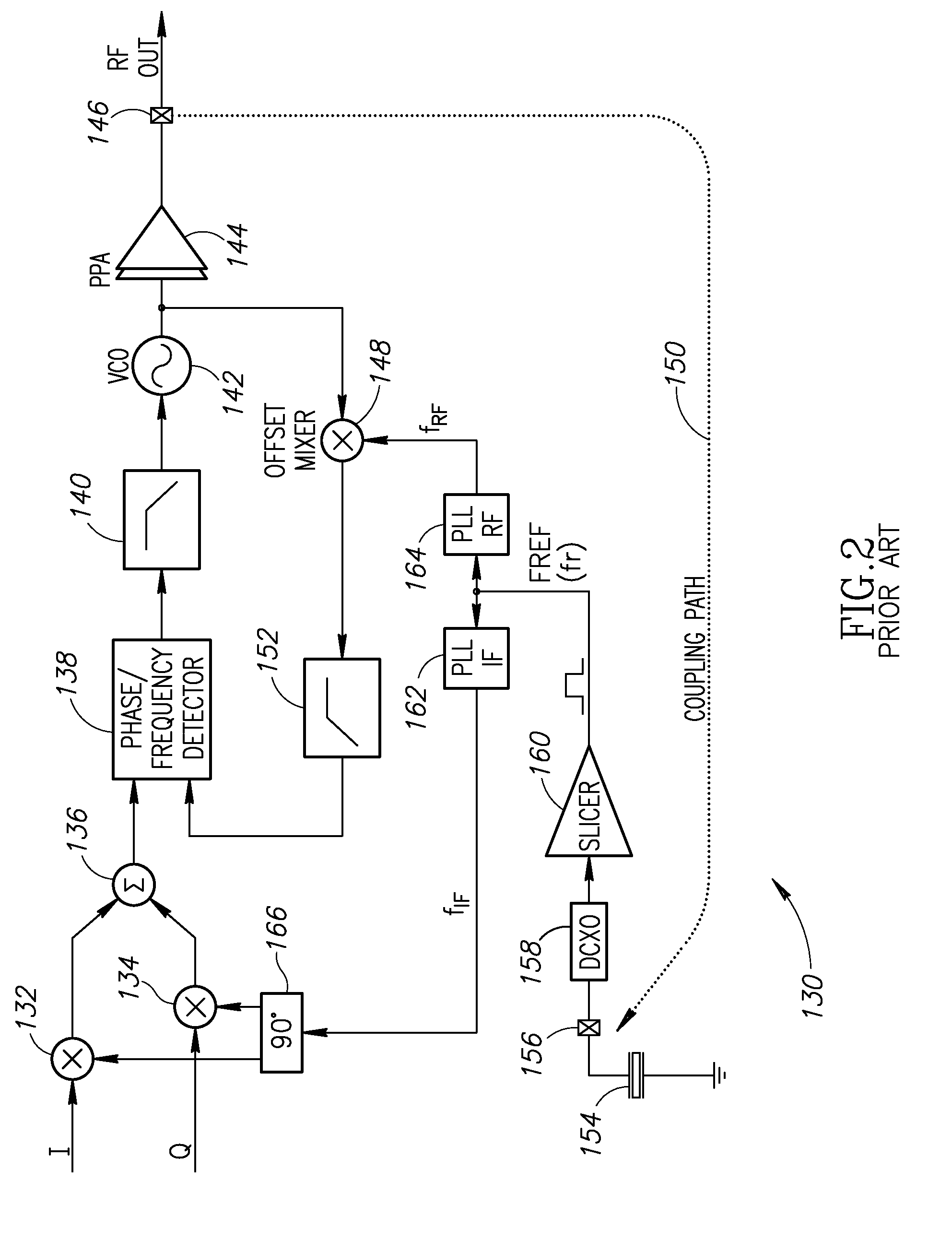

Image

Examples

Embodiment Construction

Notation Used Throughout

[0060]The following notation is used throughout this document.

TermDefinitionACAlternating CurrentACWAmplitude Control WordADCAnalog to Digital ConverterADPLLAll Digital Phase Locked LoopAMAmplitude ModulationASICApplication Specific Integrated CircuitAVIAudio Video InterfaceBISTBuilt-In Self TestBMPWindows BitmapCMOSComplementary Metal Oxide SemiconductorCPUCentral Processing UnitDBBDigital BasebandDCDirect CurrentDCODigitally Controlled OscillatorDCXODigitally Controlled Crystal OscillatorDPADigitally Controlled Power AmplifierDRACDigital to RF Amplitude ConversionDRPDigital RF Processor or Digital Radio ProcessorDSLDigital Subscriber LineDSPDigital Signal ProcessorEDGEEnhanced Data Rates for GSM EvolutionEDREnhanced Data RateEPROMErasable Programmable Read Only MemoryFCWFrequency Command WordFIBFocused Ion BeamFMFrequency ModulationFPGAField Programmable Gate ArrayGMSKGaussian Minimum Shift KeyingGPSGlobal Positioning SystemGSMGlobal System for Mobile commu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More