Methods and systems for controlling accumulation of electrical charge during semiconductor etching processes

a technology of electrical charge and etching process, which is applied in the direction of semiconductor/solid-state device testing/measurement, fluid pressure measurement, instruments, etc., can solve the problem of charge-induced damage occurring during plasma etching process, the most frequent type of damage, and the defect or damage in the wafer that occurs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

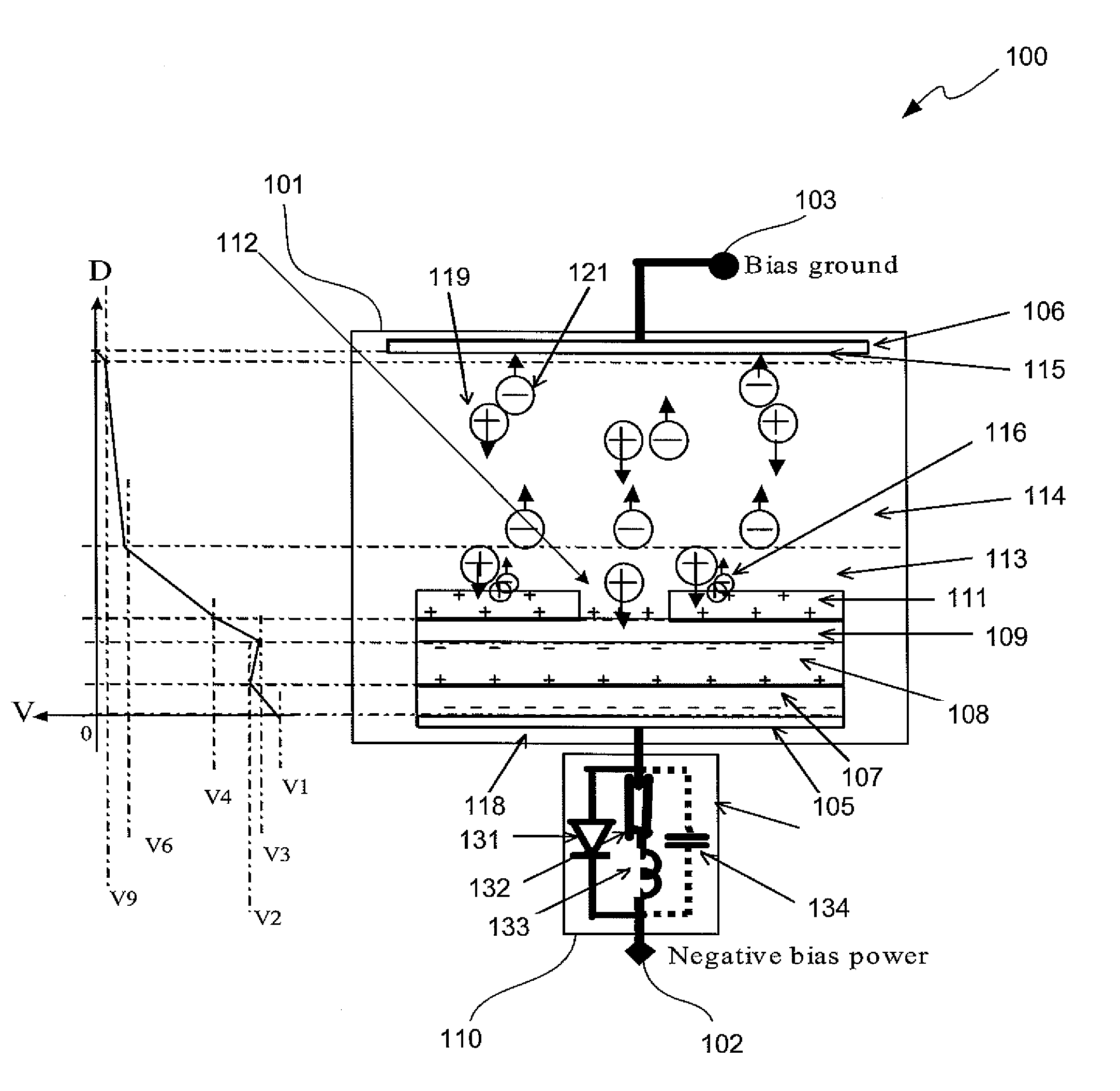

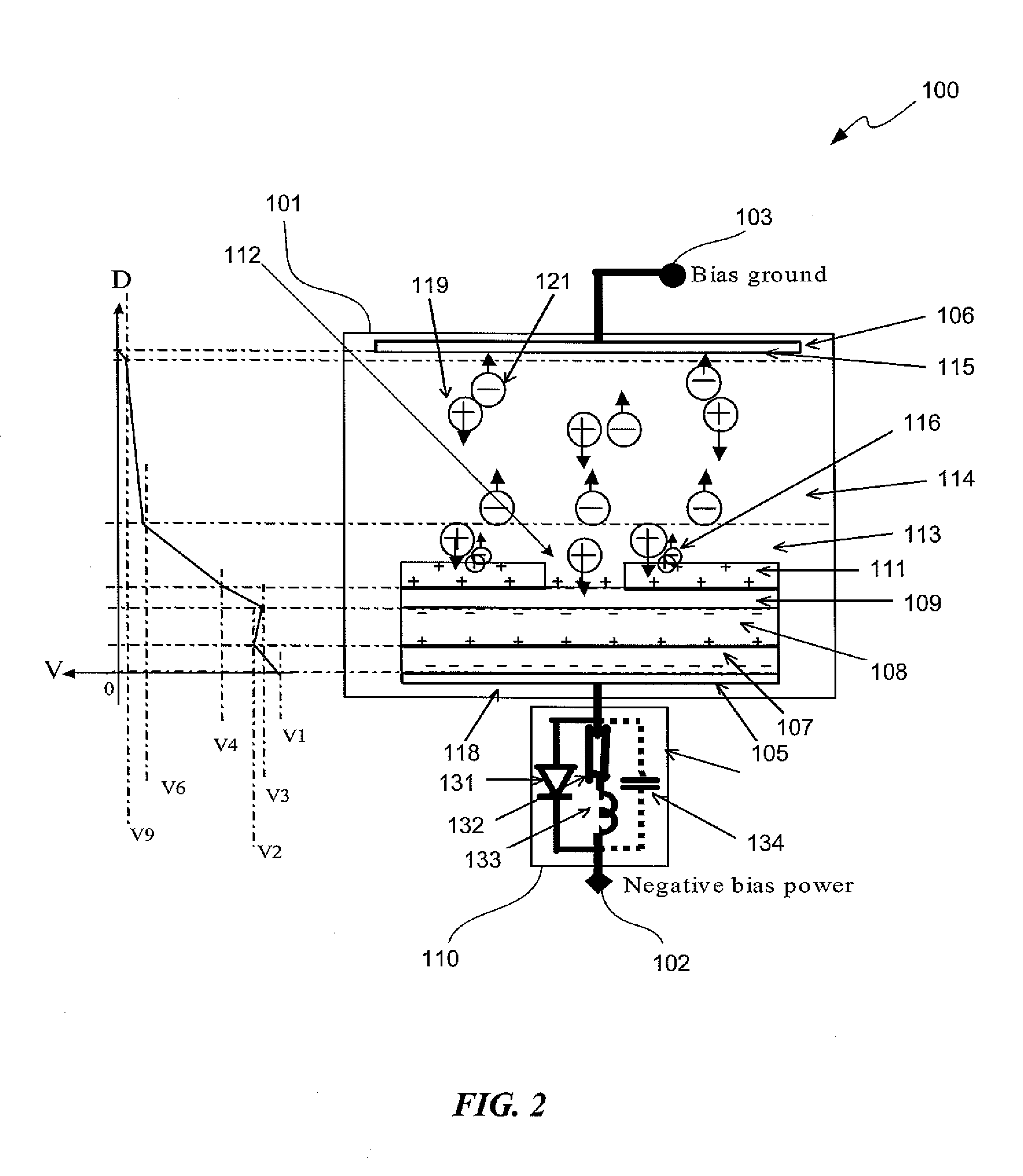

[0029]The invention provides a method and system for controlling the accumulation of electrical charge during a semiconductor plasma etching process performed in a plasma etching chamber. In accordance with the invention, the bias voltage supplied to the plasma etching chamber is modulated by a bias power modulation circuit to control the accumulation of electrical charge and to force the accumulated electrical charge to be periodically discharged at a controlled rate of discharge that prevents the wafer from being damaged. The manner in which this is accomplished in accordance with an illustrative embodiment will now be described with reference to FIGS. 2-5.

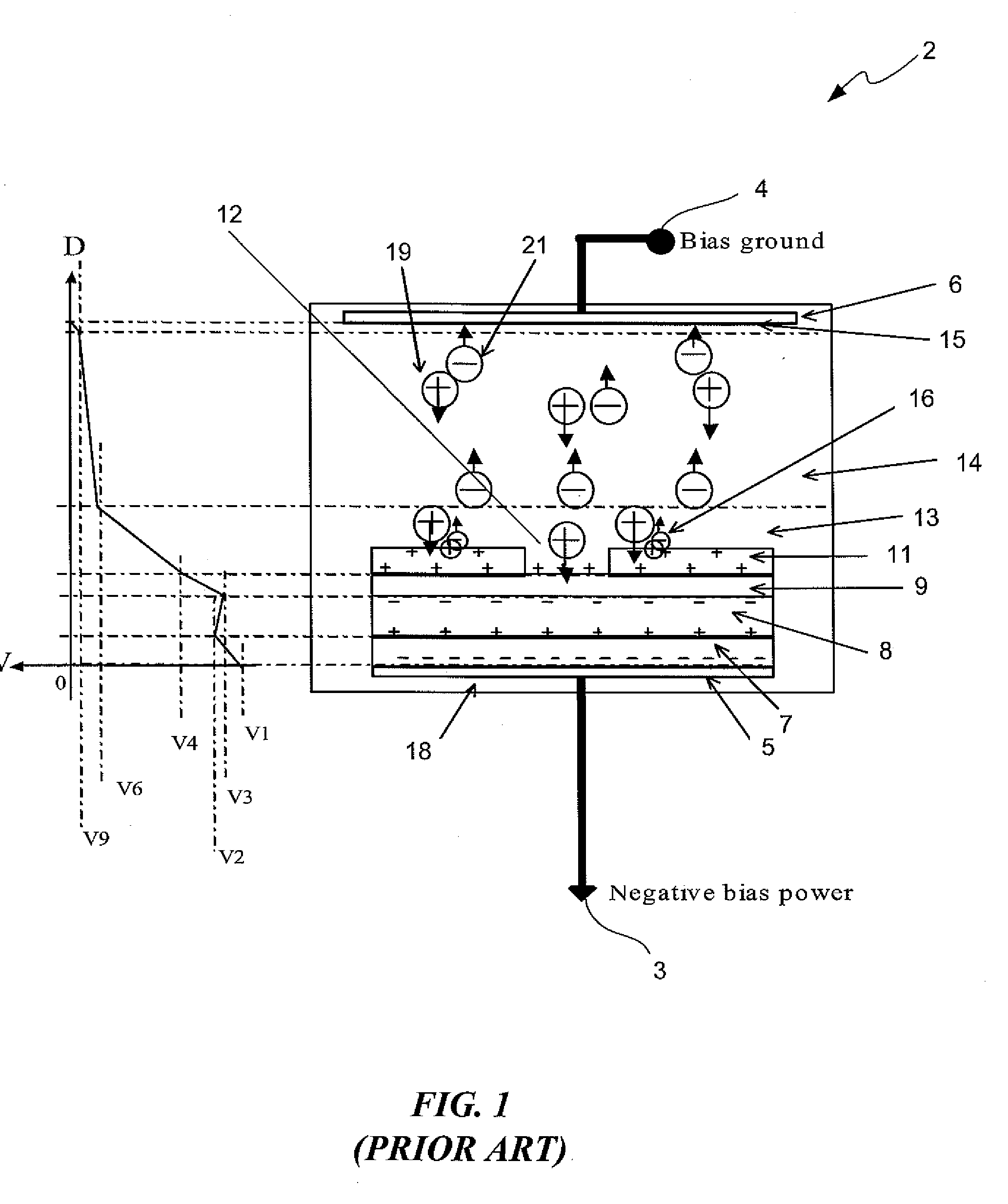

[0030]FIG. 2 illustrates a block diagram of a plasma etching system 100 equipped with a bias power modulation circuit 110 in accordance with an illustrative embodiment of the invention. The system 100 includes a chamber 101 that has a negative bias power terminal 102 and a bias ground terminal 103 electrically coupled to it. Ref...

PUM

| Property | Measurement | Unit |

|---|---|---|

| voltage | aaaaa | aaaaa |

| electrical charge | aaaaa | aaaaa |

| frequency | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More