Method of fabricating circuit board

a circuit board and fabrication method technology, applied in the direction of printed circuit manufacturing, superimposed coating process, coating, etc., can solve the problems of insufficient polishing, short circuit, and inability to flow specified current in the wiring, so as to suppress the occurrence of defocus, reduce roll-off, and suppress the effect of lack of cutting or excessive cutting of the conductor layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example

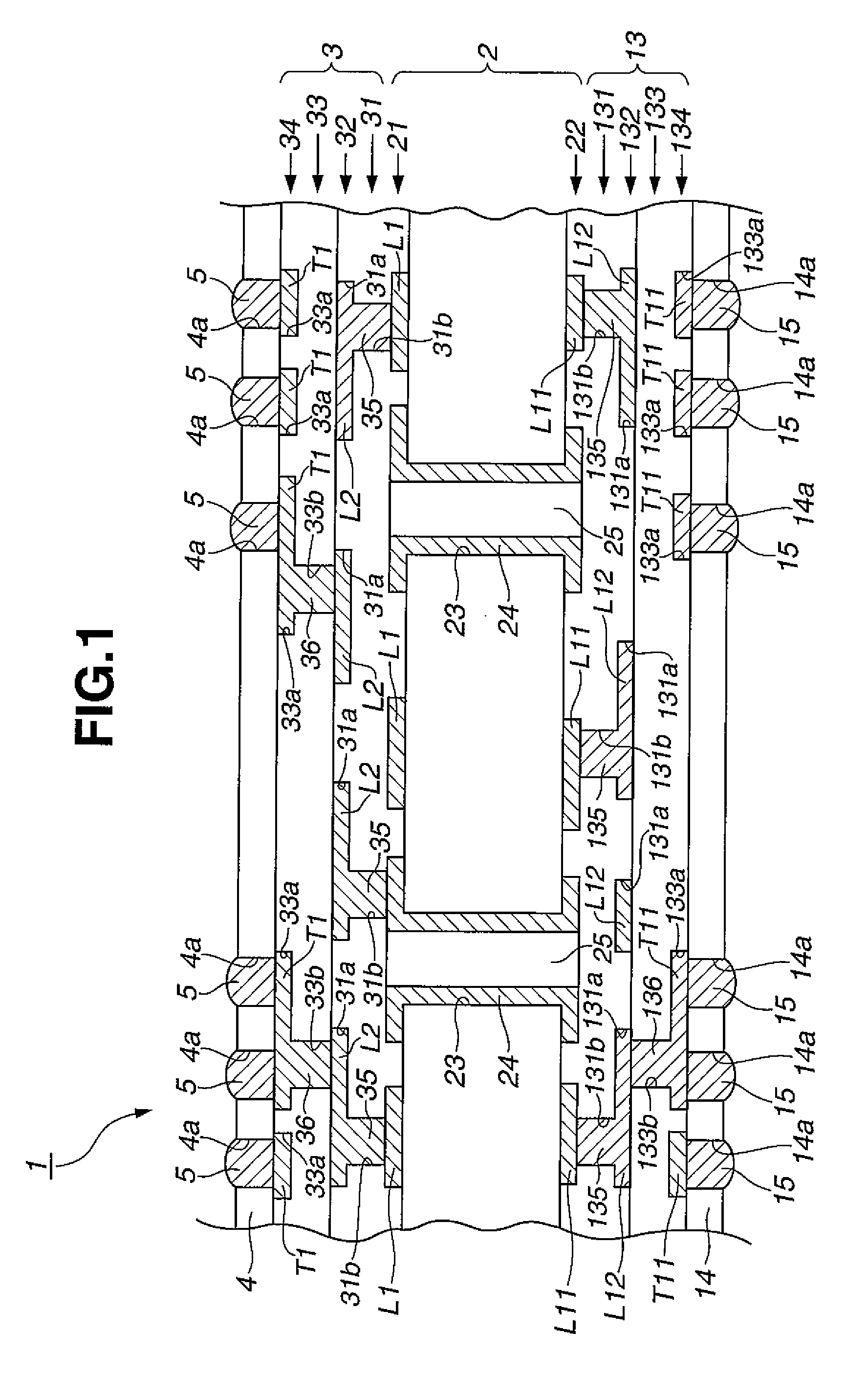

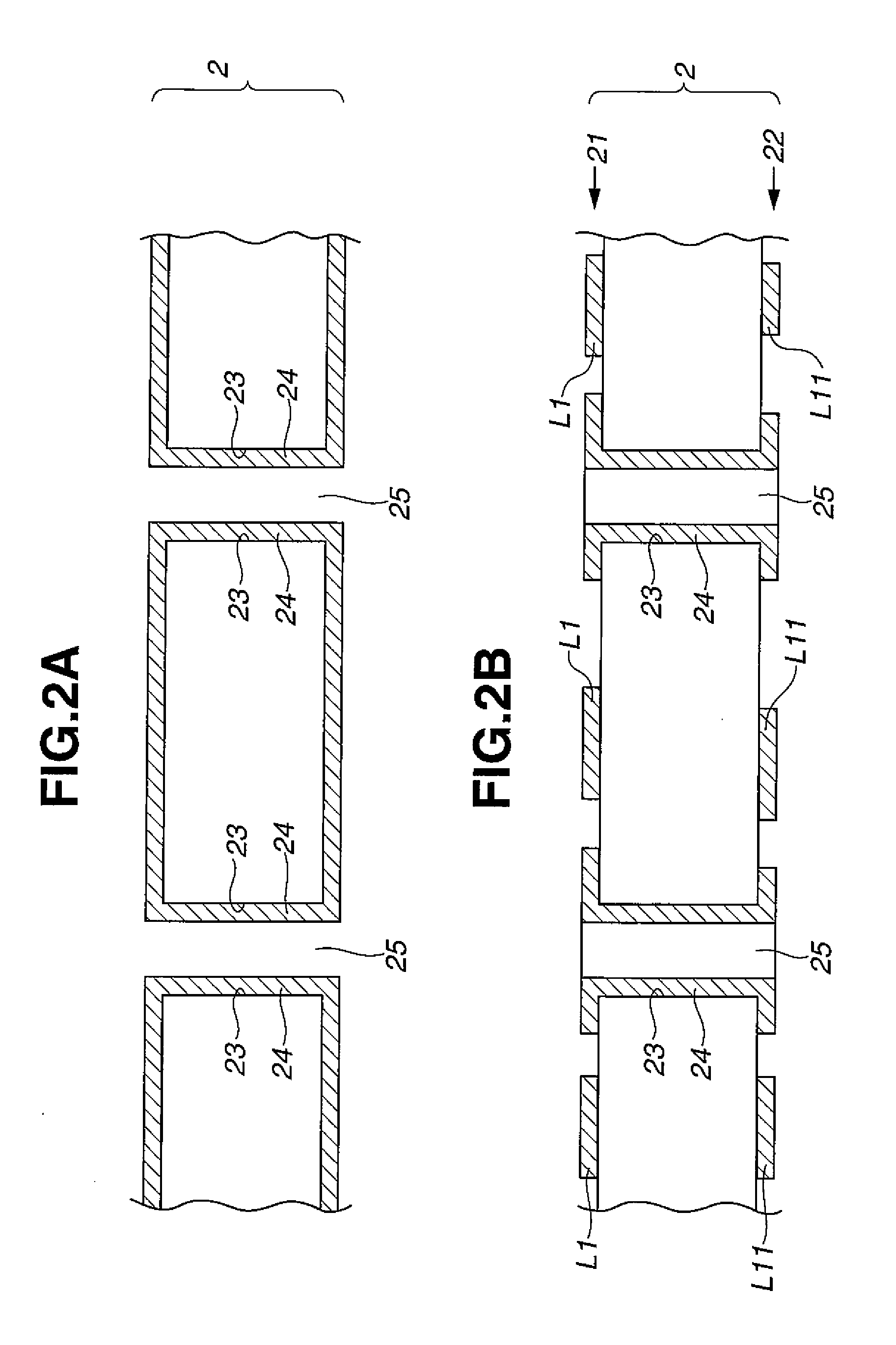

[0057]Next, an example of the method of fabricating the circuit board 1 of the present invention is explained. In the example, in accordance with the fabricating method as described above, a test piece was prepared by forming a copper plating layer embedded in a wiring trench in a resin insulation layer, and then subjecting the copper plating layer to cutting with a diamond bite. A cut surface of the thus obtained test piece was observed by a SEM.

[0058](Preparation of Test Piece)

An insulating film made of a resin material containing an epoxy resin as a main component was laminated on a surface of a plate-like resin substrate as a core substrate to thereby form a laminate. Thus obtained laminate was pressed under heating using a vacuum compression-bonding hot press so that the insulating resin film was compression-bonded to the core substrate while being heat-cured. Next, the laminate was subjected to laser irradiation with a laser processing machine, thereby forming a wiring trench ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| insulating | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More