Method and apparatus for aligning a clock signal and a data strobe signal in a memory system

a memory system and clock signal technology, applied in the field of method and apparatus for aligning a clock signal and a data strobe signal in a, can solve the problems of increasing the difficulty of carrying out the write levelling process, the mechanism has now been found to be not practical in the contemporary system, and the power supply noise induced jitter is more susceptible to the effect of nois

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

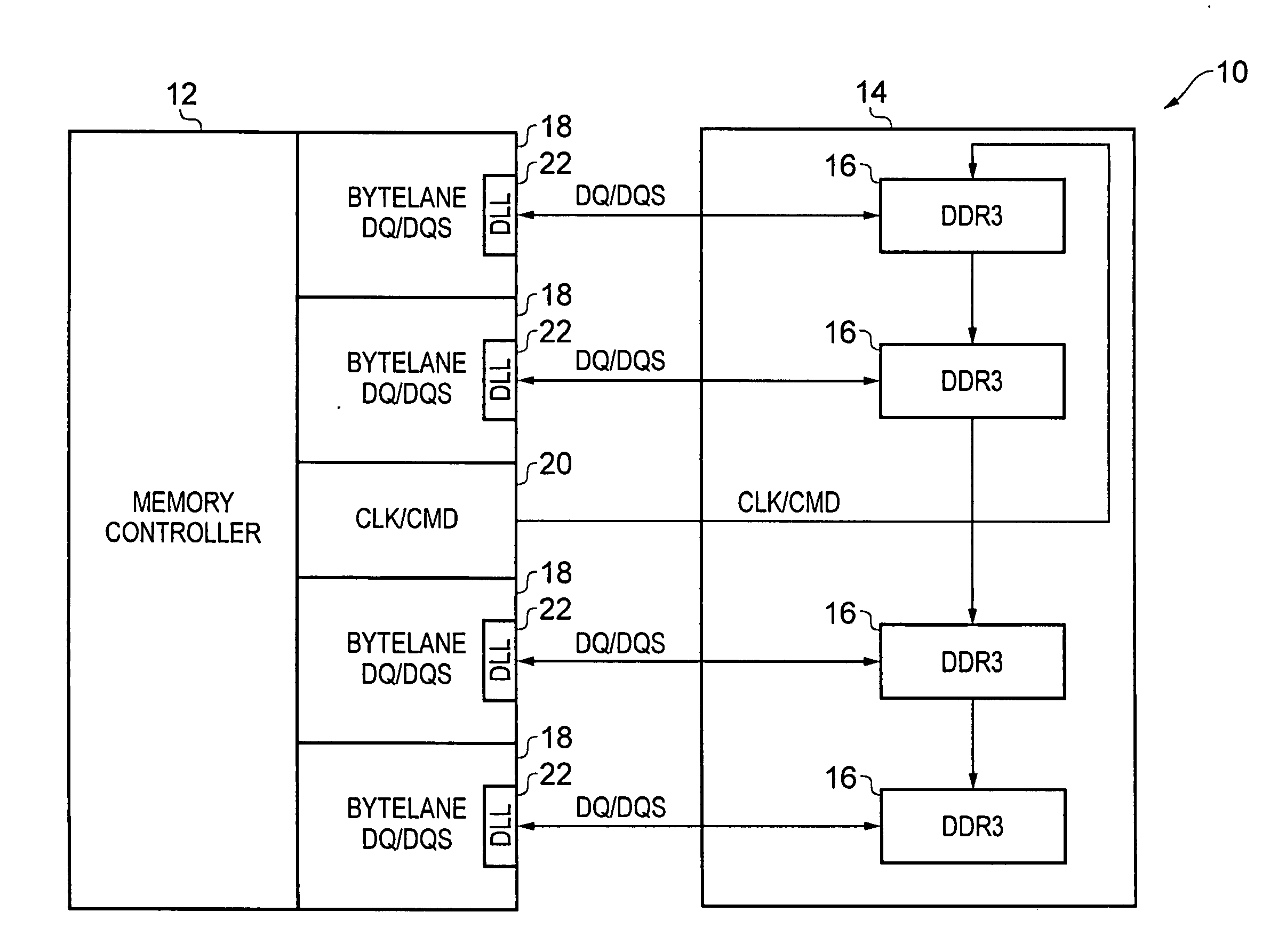

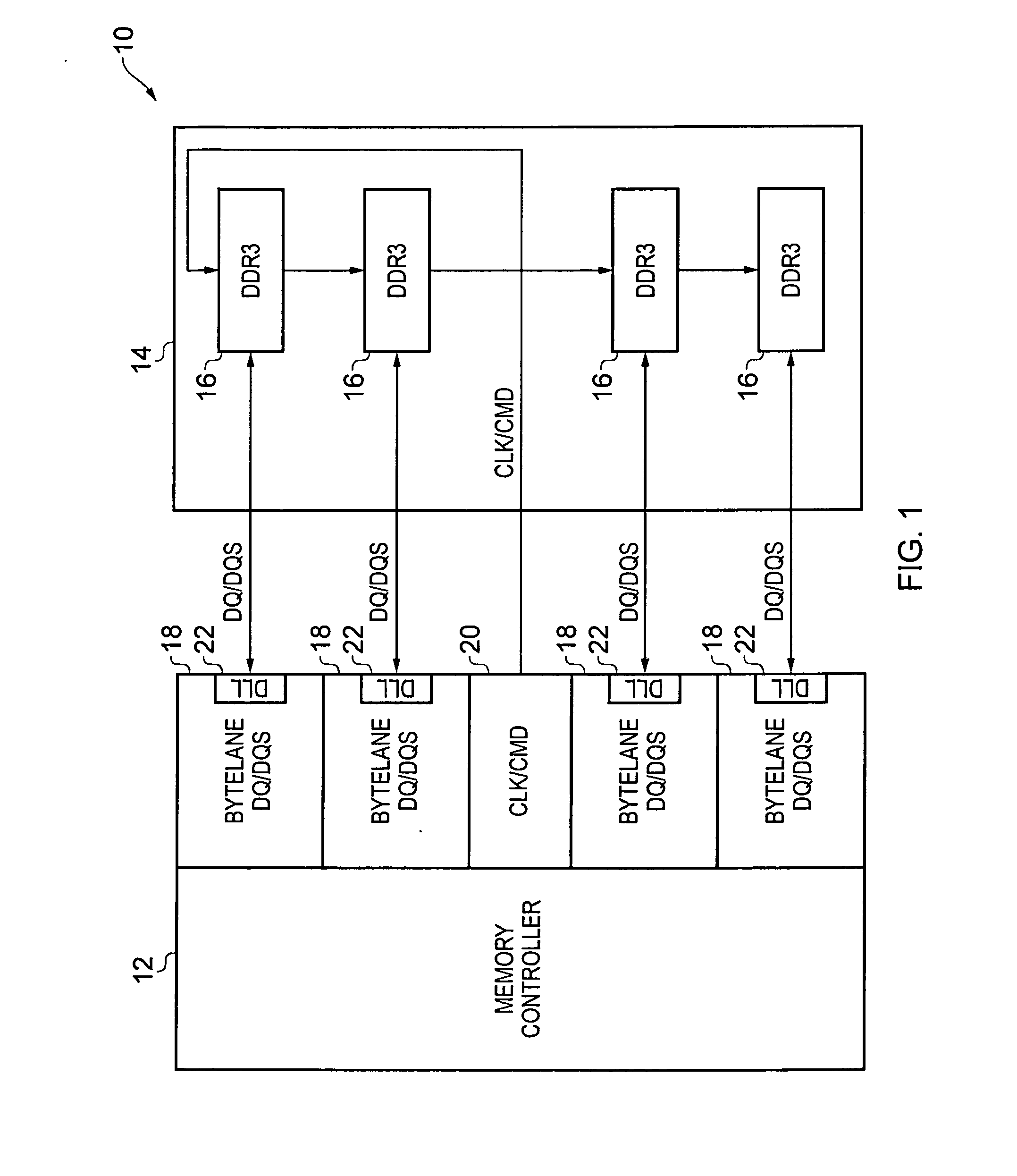

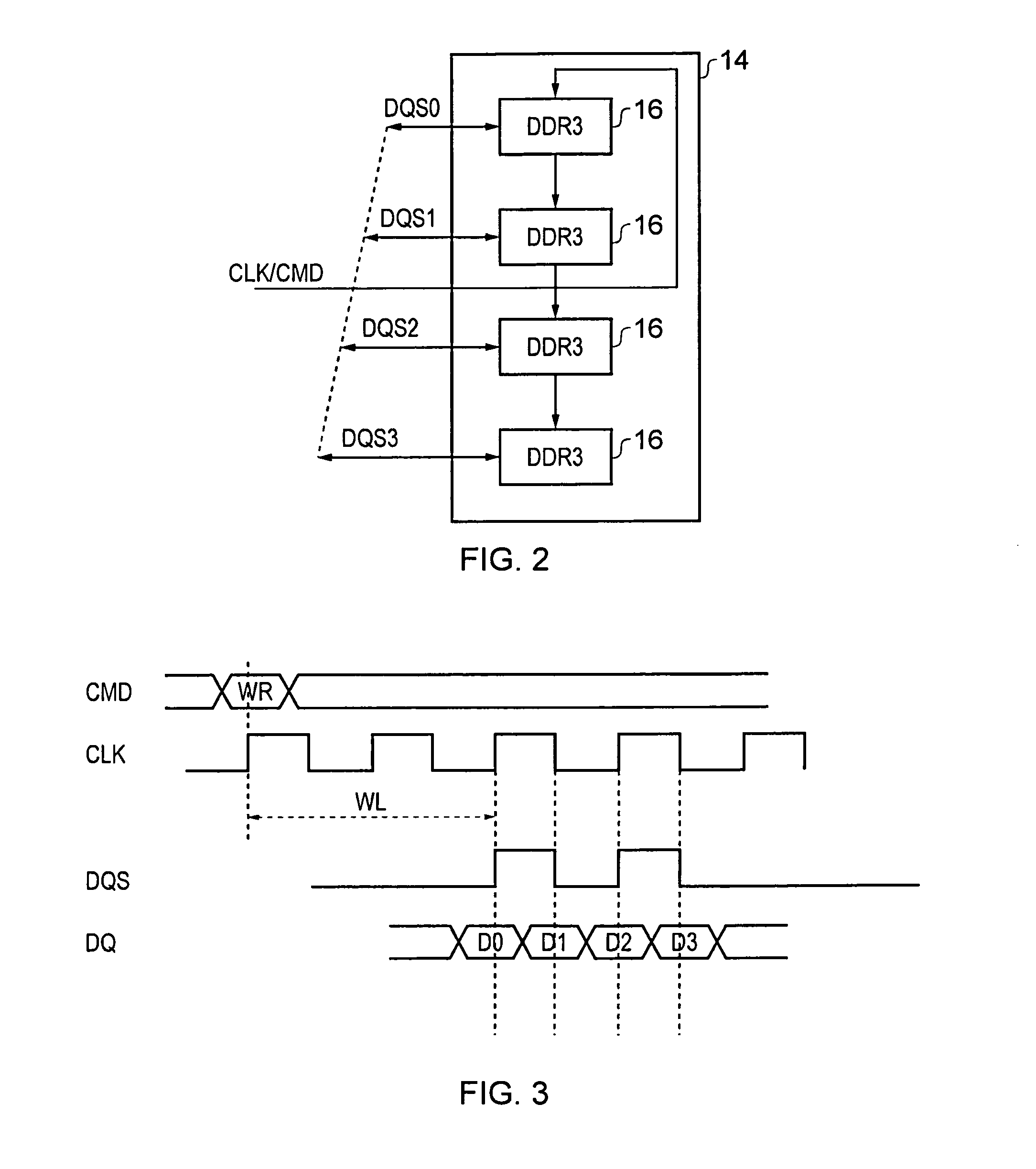

[0070]FIG. 1 schematically illustrates a DDR memory system 10, which generally comprises a memory controller integrated circuit 12 and a memory module integrated circuit 14. The memory module integrated circuit 14 comprises four DDR3 modules 16, each of which may be accessed in parallel by its own dedicated bytelane 18 provided as part of the memory controller integrated circuit 12. The memory controller integrated circuit 12 further comprises a clock / command (CLK / CMD) module 20 which is configured to transmit clock and command signals to the DDR3 modules 16. In the illustrated embodiment shown in FIG. 1, the CLK / CMD signals are transmitted between the DDR3 modules in a “fly-by” configuration to improve signal integrity (avoiding the reflections associated with a branching topology). Accordingly, the memory controller 12 can cause data to be read from one of the DDR3 modules 16 by issuing appropriate command (CMD) signals via the CLK / CMD path (in association with the clock signal CL...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More