Low threading dislocation density relaxed mismatched epilayers without high temperature growth

a dislocation density and low threading technology, applied in the direction of single crystal growth, polycrystalline material growth, chemistry apparatus and processes, etc., can solve the problems of difficult depositing high germanium concentration alloys without deleterious, problematic material combinations in processing, etc., to avoid the generation of germane particles and low threading

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

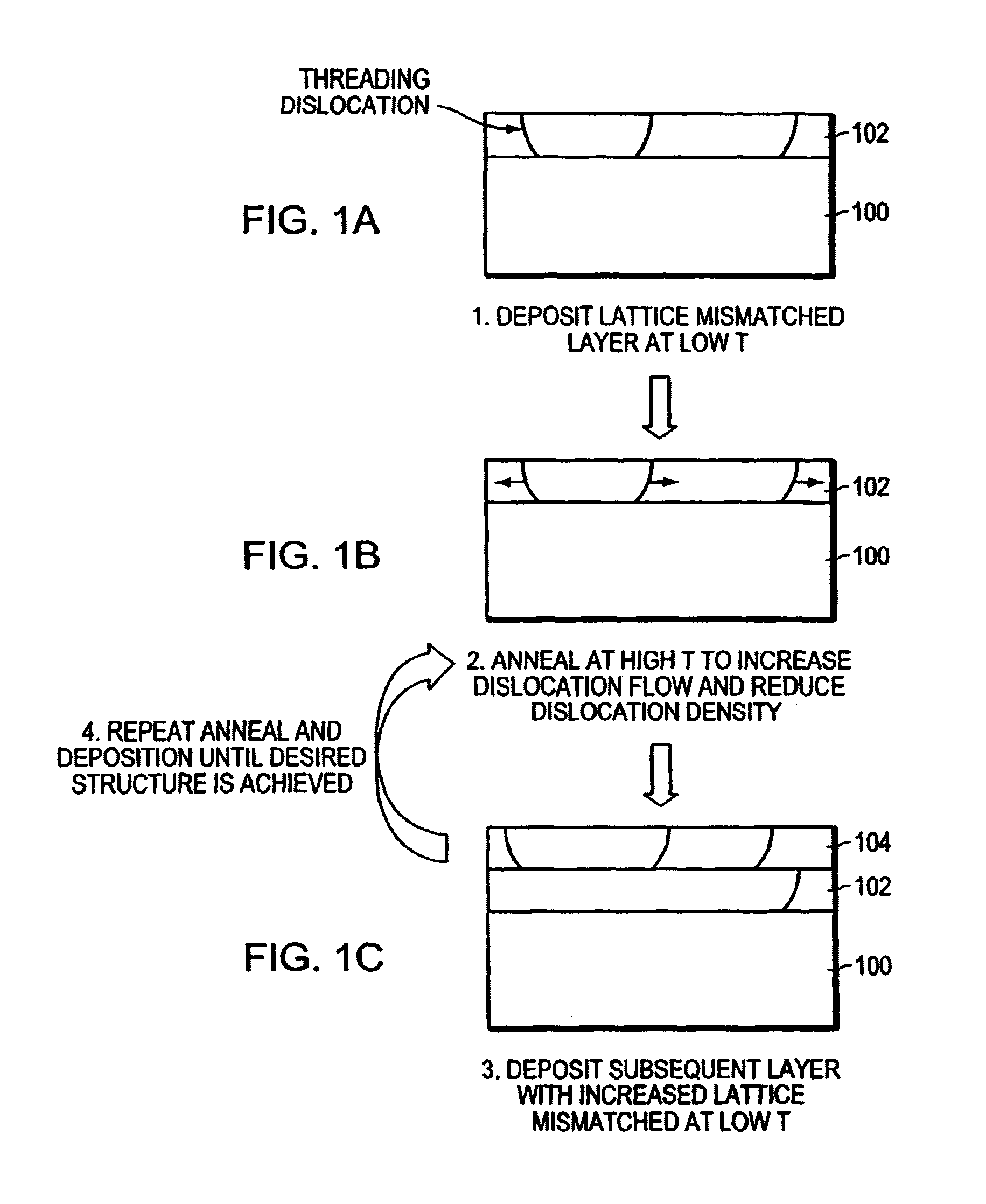

FIGS. 1A-1C is a schematic block diagram of the growth process and subsequent structure of low dislocation density, lattice mismatched films using alternating steps of epitaxial growth and high temperature annealing. In accordance with an exemplary embodiment of the invention, a relatively low lattice-mismatched film 102 is deposited on a surface of a substrate 100 with a different lattice constant at a low temperature, i.e., where particle generation is at a minimum. A low mismatched film can be defined as one in which the lattice mismatch is less than 1%.

After deposition of the film 102, the film is annealed at high temperature without any deposition source gas flowing across the surface, i.e., hydrogen or nitrogen, since they do not deposit any atoms on the surface. This annealing step increases dislocation flow and nearly completely relaxes the deposited film. Because the mismatch is low, the threading dislocation density remains low. Also, the rapid thermal feature of many CVD ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More